In earlier tutorials, we discussed the interfacing of LCD and GLCD. In this tutorial, we will see how to interfaces an I2C OLED(128x64) with 8051. There are plenty of well written arduino oled libraries for displaying strings, numbers, and logos. They all use a shadow ram buffer of 1024 bytes(128x64 pixels) and support different fonts and graphics. As 8051 has only 128 bytes of RAM we cannot use the shadow RAM buffer and cannot support all the fonts and graphics.

First, we will see the frame format for sending the commands and data to OLED. After this, we will discuss few of the OLED commands. Finally, we will be displaying string, numbers on OLED.

Displaying of logos/icons will be discussed in the separate tutorial.

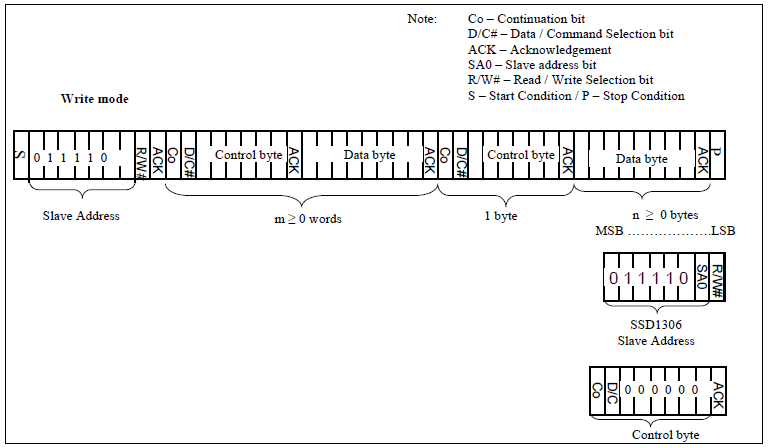

OLED Frame Format

The I2C communication interface consists of slave address bit SA0, I2C-bus data signal SDA and I2C-bus clock signal SCL. Both the data and clock signals must be connected to pull-up resistors.

- Slave address bit (SA0): SSD1306 has to recognize the slave address before transmitting or receiving any information by the I2C-bus. The device will respond to the slave address following by the slave address bit (“SA0” bit) and the read/write select bit (“R/W#” bit) with the following byte format,

| B7 | B6 | B5 | B4 | B3 | B2 | B1 | B0 |

|---|---|---|---|---|---|---|---|

| 0 | 1 | 1 | 1 | 1 | 0 | SA0 | R/W |

SA0 bit provides an extension bit for the slave address. Either “0111100” or “0111101”, can be selected as the slave address of SSD1306.

R/W bit is used to determine the operation mode of the I2C-bus interface.

R/W=1, it is in read mode.

R/W=0, it is in write mode.

- I2C-bus data signal (SDA): SDA acts as a communication channel between the transmitter and the receiver. The data and the acknowledgement are sent through the SDA.

- I2C-bus clock signal (SCL): The transmission of information in the I2C-bus is following a clock signal, SCL. Each transmission of data bit is taken place during a single clock period of SCL.

OLED Commands

The I2C-bus interface gives access to write data and command into the device. Below image shows the write mode of I2C-bus in chronological order.

- The master device initiates the data communication by a start condition. The definition of the start condition is shown in Figure 8-8. The start condition is established by pulling the SDA from HIGH to LOW while the SCL stays HIGH.

- The slave address is following the start condition for recognition use. For the SSD1306, the slave address is either “b0111100” or “b0111101” by changing the SA0 to LOW or HIGH (D/C pin acts as SA0).

- The write mode is established by setting the R/W# bit to logic “0”.

- An acknowledgement signal will be generated after receiving one byte of data, including the slave address and the R/W# bit. Please refer to the Figure 8-9 for the graphical representation of the acknowledge signal. The acknowledge bit is defined as the SDA line is pulled down during the HIGH period of the acknowledgement related clock pulse.

- After the transmission of the slave address, either the control byte or the data byte may be sent across the SDA. A control byte mainly consists of Co and D/C# bits following by six “0” ‘s.

- a. If the Co bit is set as logic “0”, the transmission of the following information will contain data bytes only.

- b. The D/C# bit determines the next data byte is acted as a command or a data. If the D/C# bit is set to logic “0”, it defines the following data byte as a command. If the D/C# bit is set to logic “1”, it defines the following data byte as a data which will be stored at the GDDRAM.

The GDDRAM column address pointer will be increased by one automatically after each data write.

- Acknowledge bit will be generated after receiving each control byte or data byte.

- The write mode will be finished when a stop condition is applied. The stop condition is also defined in Figure 8-8. The stop condition is established by pulling the “SDA in” from LOW to HIGH while the “SCL” stays HIGH.