Contents

Objective

In this tutorial, we are going to discuss the LPC2148 UART communication. LPC2148 has two inbuilt USARTs. We are going to discuss the only UART0. After this tutorial, you should be able to extend it to UART1.

After understating the basics of LPC2148 UART module, We will discuss how to use the ExploreEmbedded libraries to communicate with any of the UART devices.

For more info on UART/RS232 check 8051 tutorial.

UART module

UART module and registers.

LPC1768 has 4-UARTs numbering 0-3, similarly, the pins are also named as RXD0-RXD3 and TXD0-TXD3.As the LPC1768 pins are multiplexed for multiple functionalities, first they have to be configured as UART pins.

Below table shows the multiplexed UART's pins.

| Port Pin | Pin Number | PINSEL_FUNC_0 | PINSEL_FUNC_1 | PINSEL_FUNC_2 | PINSEL_FUNC_3 |

|---|---|---|---|---|---|

| P0.02 | 98 | GPIO | TXD0 | ADC0[7] | |

| P0.03 | 99 | GPIO | RXD0 | ADC0[6] | |

| P2_0 | 48 | GPIO | PWM1[1] | TXD1 | |

| P0.1 | 49 | GPIO | PWM1[2] | RXD1 | |

| P0.10 | 62 | GPIO | TXD2 | SDA2 | MAT3[0] |

| P0.11 | 63 | GPIO | RXD2 | SCL2 | MAT3[1] |

| P0.0 | 82 | GPIO | CAN1_Rx | TXD3 | SDA1 |

| P0.1 | 85 | GPIO | CAN1_Tx | RXD3 | SCL1 |

UART Registers

The below table shows the registers associated with LPC1768 UART.

| Register | Description |

|---|---|

| RBR | Contains the recently received Data |

| THR | Contains the data to be transmitted |

| FCR | FIFO Control Register |

| LCR | Controls the UART frame formatting(Number of Data Bits, Stop bits) |

| DLL | Least Significant Byte of the UART baud rate generator value. |

| DLM | Most Significant Byte of the UART baud rate generator value. |

UART Register Configuration

Now lets see how to configure the individual registers for UART communication.

FCR ( FIFO Control Register )

LPC1768 has inbuilt 16byte FIFO for Receiver/Transmitter. Thus it can store 16-bytes of data received on UART without overwriting. If the data is not read before the Queue(FIFO) is filled then the new data will be lost and the OVERRUN error bit will be set.

| FCR | ||||||

| 31:8 | 7:6 | 5:4 | 3 | 2 | 1 | 0 |

| RESERVED | RX TRIGGER | RESERVED | DMA MODE | TX FIFO RESET | RX FIFO RESET | FIFO ENABLE |

Bit 0 – FIFO:

This bit is used to enable/disable the FIFO for the data received/transmitted.

0--FIFO is Disabled.

1--FIFO is Enabled for both Rx and Tx.

Bit 1 – RX_FIFO:

This is used to clear the 16-byte Rx FIFO.

0--No impact.

1--CLears the 16-byte Rx FIFO and the resets the FIFO pointer.

Bit 2 – Tx_FIFO:

This is used to clear the 16-byte Tx FIFO.

0--No impact.

1--Clears the 16-byte Tx FIFO and the resets the FIFO pointer.

Bit 3 – DMA_MODE:

This is used for Enabling/Disabling DMA mode.

0--Disables the DMA.

1--Enables DMA only when the FIFO(bit-0) bit is SET.

Bit 7:6 – Rx_TRIGGER:

This bit is used to select the number of bytes of the receiver data to be written so as to enable the interrupt/DMA.

00-- Trigger level 0 (1 character or 0x01)

01-- Trigger level 1 (4 characters or 0x04)

10-- Trigger level 2 (8 characters or 0x08)

11-- Trigger level 3 (14 characters or 0x0E)

LCR ( Line Control Register )

This register is used for defining the UART frame format ie. Number of Data bits, STOP bits etc.

| LCR | ||||||

| 31:8 | 7 | 6 | 5:4 | 3 | 2 | 1:0 |

| Reserved | DLAB | Break COntrol | Parity Select | Parity Enable | Stop Bit Select | Word Length Select |

Bit 1:0 – WLS : WordLenghtSelect

These two bits are used to select the character length

00-- 5-bit character length

01-- 6-bit character length

10-- 7-bit character length

11-- 8-bit character length

Bit 2 – Stop Bit Selection:

This bit is used to select the number(1/2) of stop bits

0-- 1 Stop bit

1-- 2 Stop Bits

Bit 3 – Parity Enable:

This bit is used to Enable or Disable the Parity generation and checking.

0-- Disable parity generation and checking.

1-- Enable parity generation and checking.

Bit 5:4 – Parity Selection:

These two bits will be used to select the type of parity.

00-- Odd parity. Number of 1s in the transmitted character and the attached parity bit will be odd.

01-- Even Parity. Number of 1s in the transmitted character and the attached parity bit will be even.

10-- Forced "1" stick parity.

11-- Forced "0" stick parity

Bit 6 – Break Control

0-- Disable break transmission.

1-- Enable break transmission. Output pin UARTn TXD is forced to logic 0

Bit 8 – DLAB: Divisor Latch Access Bit

This bit is used to enable the access to divisor latch.

0-- Disable access to divisor latch

0-- Enable access to divisor latch

LSR (Line Status Register)

The is a read-only register that provides status information of the UART TX and RX blocks.

| LSR | ||||||||

| 31:8 | 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| Reserved | RXFE | TEMT | THRE | BI | FE | PE | OE | RDR |

Bit 0 – RDR: Receive Data Ready

This bit will be set when there is a received data in RBR register. This bit will be automatically cleared when RBR is empty.

0-- The UARTn receiver FIFO is empty.

1-- The UARTn receiver FIFO is not empty.

Bit 1 – OE: Overrun Error

The overrun error condition is set when the UART Rx FIFO is full and a new character is received.

In this case, the UARTn RBR FIFO will not be overwritten and the character in the UARTn RSR will be lost.

0-- No overrun

1-- Buffer over run

Bit 2 – PE: Parity Error

This bit is set when the receiver detects a error in the Parity.

0-- No Parity Error

1-- Parity Error

Bit 3 – FE: Framing Error

This bit is set when there is error in the STOP bit(LOGIC 0)

0-- No Framing Error

1-- Framing Error

Bit 4 – BI: Break Interrupt

This bit is set when the RXDn is held in the spacing state (all zeroes) for one full character transmission

0-- No Break interrupt

1-- Break Interrupt detected.

Bit 5 – THRE: Transmitter Holding Register Empty

THRE is set immediately upon detection of an empty THR. It is automatically cleared when the THR is written.

0-- THR register is Empty

1-- THR has valid data to be transmitted

Bit 6 – TEMT: Transmitter Empty

TEMT is set when both UnTHR and UnTSR are empty; TEMT is cleared when any of them contain valid data.

0-- THR and/or the TSR contains valid data.

1-- THR and the TSR are empty.

Bit 7 – RXFE: Error in Rx FIFO

This bit is set when the received data is affected by Framing Error/Parity Error/Break Error.

0-- RBR contains no UARTn RX errors.

1-- RBR contains at least one RX error.

TER (Transmitter Enable register)

This register is used to Enable/Disable the transmission

| TER | ||

| 31:8 | 7 | 6-0 |

| Reserved | TXEN | Reserved |

Bit 7 – TXEN: Trsnamitter Enable

When this bit is 1, the data written to the THR is output on the TXD pin.

If this bit is cleared to 0 while a character is being sent, the transmission of that character is completed, but no further characters are sent until this bit is set again.

In other words, a 0 in this bit blocks the transfer of characters.

- Note: By default this bit will be set after Reset.

Baudrate Calculation

LPC1768 generates the baud rate depending on the values of DLM,DLL.

Baudrate = PCLK/ (16 * ( 256 * DLM + DLL) * (1+ DivAddVal/MulVal))

Getting the PCLK value.

PCLKSELx registers contains the PCLK info for all the clock dependent peripherals in which Bit6,Bit7 contains the Uart Clock(ie.UART_PCLK) information.

The UART_PCLK and the actual Peripheral Clock(PCLK) is calculated as below.

(Refer data sheet for more info)

| UART_PCLK | PCLK |

| 0 | SystemFreq/4 |

| 1 | SystemFreq |

| 2 | SystemFreq/2 |

| 3 | SystemFreq/8 |

DivAddVal/MulVal == 0

Using the above parameters , DLL/DLM is calculated as below.

(256 * DLL + DLM) = PCLK / (16* Baudrate).

Steps for Configuring UART0

Below are the steps for configuring the UART0.

- Step1: Configure the GPIO pin for UART0 function using PINSEL register.

- Step2: Configure the FCR for enabling the FIXO and Reste both the Rx/Tx FIFO.

- Step3: Configure LCR for 8-data bits, 1 Stop bit, Disable Parity and Enable DLAB.

- Step4: Get the PCLK from PCLKSELx register 7-6 bits.

- Step5: Calculate the DLM,DLL vaues for required baudrate from PCLK.

- Step6: Updtae the DLM,DLL with the calculated values.

- Step6: Finally clear DLAB to disable the access to DLM,DLL.

After this the UART will be ready to Transmit/Receive Data at the specified baudrate.

Code sniffet:

Steps for transmitting a char

- Step1: Wait till the previous char is transmitted ie. till THRE becomes high.

- Step2: Load the new char to be transmitted into THR.

Code snippet

Steps for Receiving a char

- Step1: Wait till the a char is received ie. till RDR becomes high.

- Step2: Copy the received data from receive buffer(RBR).

Code snippet

Code

Example 1

Below is the code for transmitting and receiving chars at 9600 baud

Using Explore Embedded Libraries

In the above tutorial we discussed how to configure and use the inbuilt LPC1768 UART.

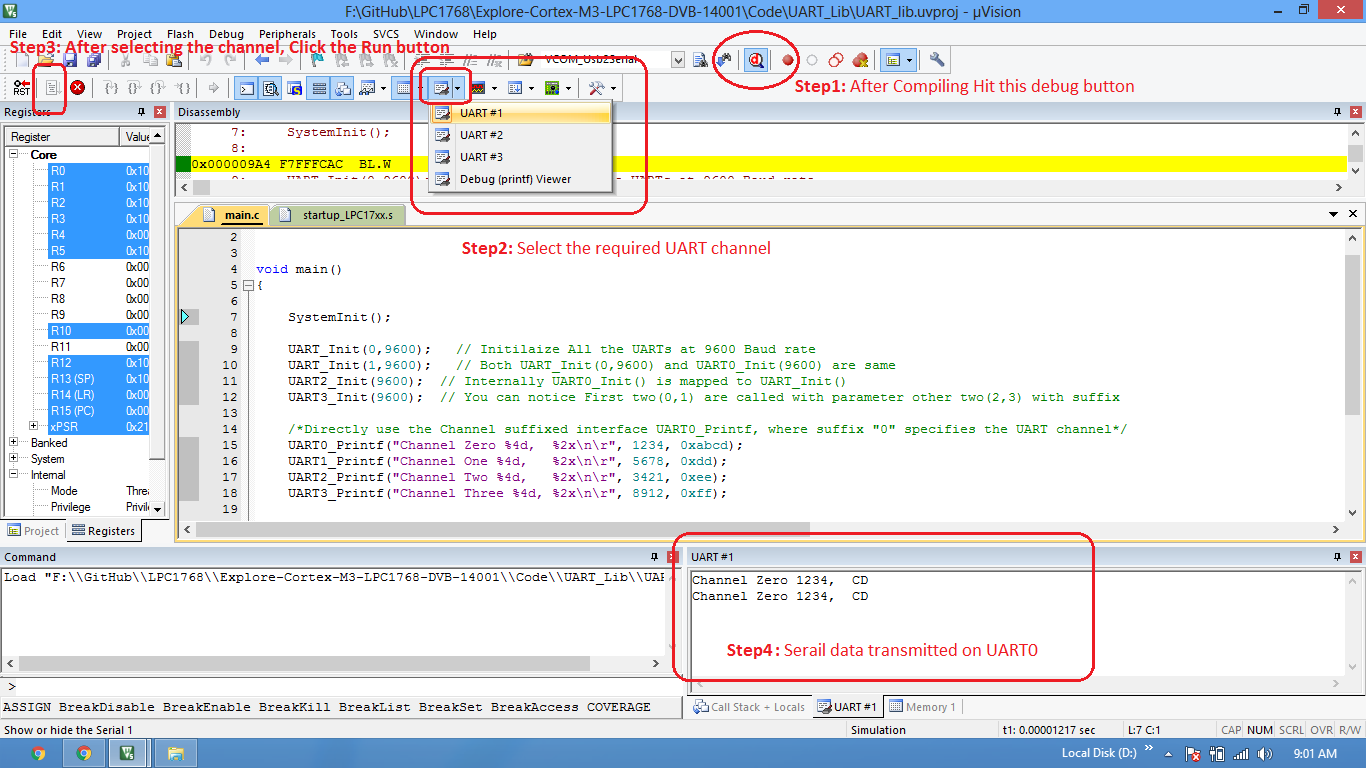

Now we will see how to use the ExploreEmbededd UART libraries to communicate on all the four UART channels.

For this you have to include the uart.c/uart.h files and associated gpio/stdutils files.

As LPC1768 has four inbuilt UART channels, the interfaces are suffixed with channel number as shown below.

UART0_Printf()

UART1_Printf()

UART2_Printf()

UART3_Printf()

- Note:Refer the uart.h file for more info.

Testing

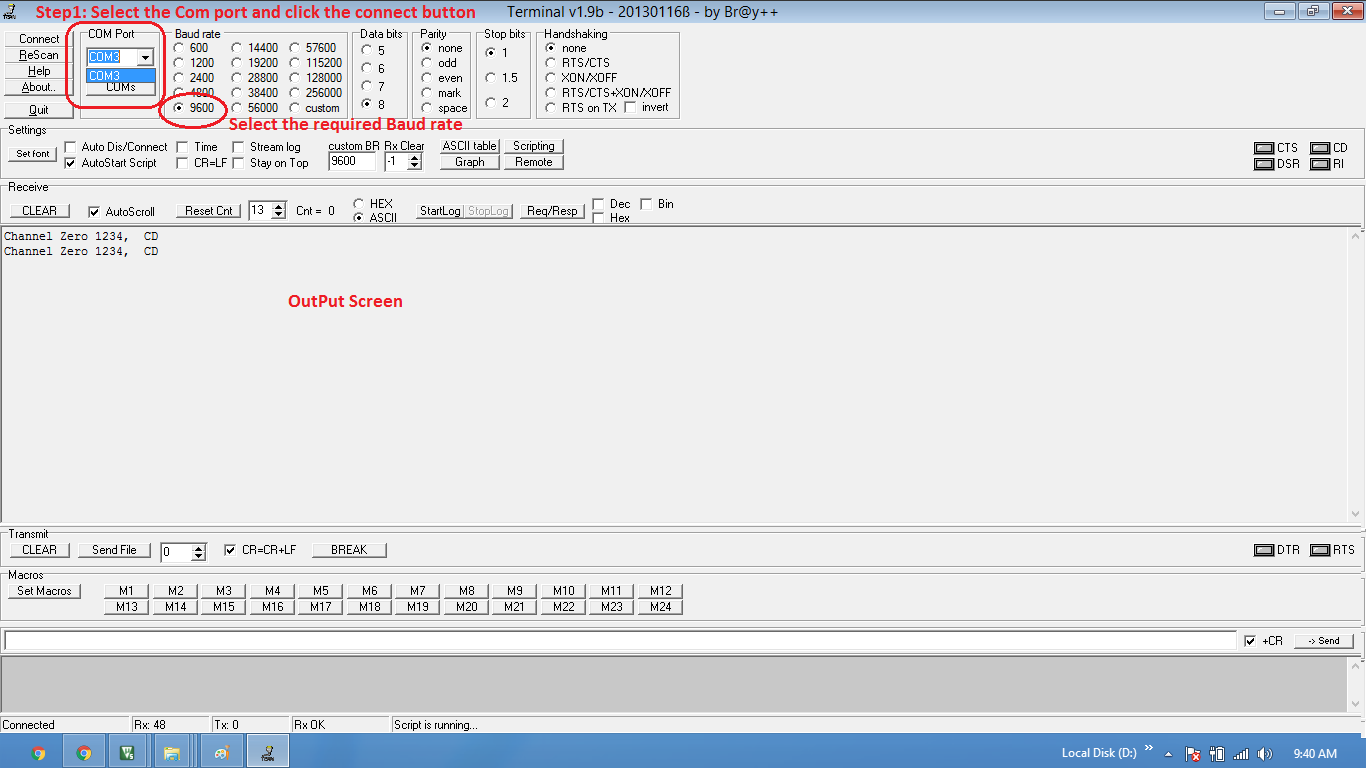

Using the Terminal Software

After generating the hex/bin file, flash it to the controller. Now connect the LPC1768 to your system using a Usb to Serial converter.

Open the terminal software , select the COM port, set baud rate and hit the connect button.

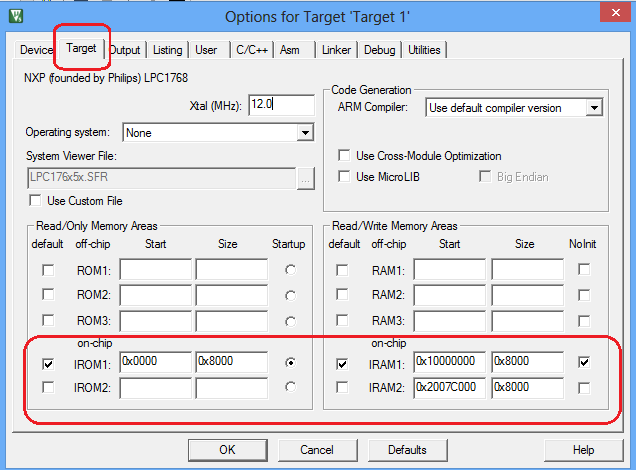

Using The Keil Simulator

Code can be tested on the Keil simulator as well. For this the target memory options needs to be set to default as shown below.

Now Rebuild the project and Run the code using the Keil simulator as shown below.

Downloads

Download the complete project folder from the below link:

https://codeload.github.com/ExploreEmbedded/Explore-Cortex-M3-LPC1768-Stick-DVB-14001/zip/master

Have a opinion, suggestion , question or feedback about the article let it out here!