Difference between revisions of "ALU in Detail"

| Line 2: | Line 2: | ||

{{box|type=l_green_light|text= You should have heard of an Arithmetic and Logic Unit before, while discussing a Computer CPU or a micro controller. In this tutorial we will look at what an ALU really is? <br /> | {{box|type=l_green_light|text= You should have heard of an Arithmetic and Logic Unit before, while discussing a Computer CPU or a micro controller. In this tutorial we will look at what an ALU really is? <br /> | ||

We will discuss a 4 bit ALU; this would limit many possibilities 16. We would assume that associated registers and instruction set are also 4 bit.<br /> | We will discuss a 4 bit ALU; this would limit many possibilities 16. We would assume that associated registers and instruction set are also 4 bit.<br /> | ||

| + | |||

| + | |||

| + | === The basic Unit: 1 bit ALU=== | ||

| + | |||

| + | [[File:1bitALU.jpg|400x350px|framed]] | ||

| + | We assume you are familiar with logic gates, and also have come across a 1 bit adder. It simple adds two 1 bit inputs as shown below. | ||

| + | |||

| + | }} | ||

{| class="wikitable" style="text-align:center" | {| class="wikitable" style="text-align:center" | ||

|- | |- | ||

| Line 17: | Line 25: | ||

|- | |- | ||

|} | |} | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

Revision as of 11:58, 8 December 2013

Arithmetic and Logic Unit in Detail

You should have heard of an Arithmetic and Logic Unit before, while discussing a Computer CPU or a micro controller. In this tutorial we will look at what an ALU really is?

We will discuss a 4 bit ALU; this would limit many possibilities 16. We would assume that associated registers and instruction set are also 4 bit.

We will discuss a 4 bit ALU; this would limit many possibilities 16. We would assume that associated registers and instruction set are also 4 bit.

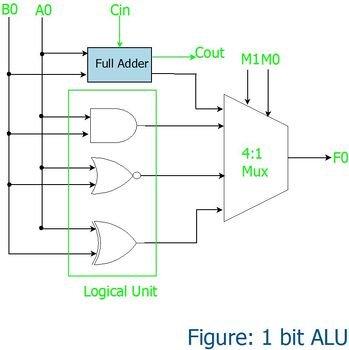

The basic Unit: 1 bit ALU

We assume you are familiar with logic gates, and also have come across a 1 bit adder. It simple adds two 1 bit inputs as shown below.

| Inputs | Outputs | ||

|---|---|---|---|

| A | B | S | C |

| 0 | 0 | 0 | 0 |

| 1 | 0 | 1 | 0 |

| 0 | 1 | 1 | 0 |

| 1 | 1 | 0 | 1 |