Difference between revisions of "LPC1768: Keil Project For Bin File"

| (4 intermediate revisions by the same user not shown) | |||

| Line 27: | Line 27: | ||

<html> | <html> | ||

<script src="https://gist.github.com/SaheblalBagwan/cb2cf78aadc724737d79.js"></script> | <script src="https://gist.github.com/SaheblalBagwan/cb2cf78aadc724737d79.js"></script> | ||

| + | </html> | ||

| + | <br> | ||

| + | <html> | ||

| + | <script src="https://gist.github.com/SaheblalBagwan/fe401523c97e4cb2d7e98565e1bd3b06.js"></script> | ||

</html> | </html> | ||

<br> | <br> | ||

| Line 49: | Line 53: | ||

[[File:Lpc1768_Keil_13.png]]<br><br> | [[File:Lpc1768_Keil_13.png]]<br><br> | ||

| − | <b>Step14:</b> Set IROM1 start address as 0x2000. Bootloader will be stored from 0x0000-0x2000 so application | + | <b>Step14:</b> Set IROM1 start address as 0x2000. Bootloader will be stored from 0x0000-0x2000 so application should start from 0x2000<br> |

[[File:Lpc1768_Keil_21.png]]<br><br> | [[File:Lpc1768_Keil_21.png]]<br><br> | ||

| Line 66: | Line 70: | ||

<br><br> | <br><br> | ||

| − | =Uploading the | + | =Uploading the Bin file= |

| − | After generating the .bin file check | + | After generating the .bin file check this tutorial for [[LPC1768: Uploading Hex and Bin files|Uploading Hex and Bin files.]]. |

<br><br> | <br><br> | ||

Latest revision as of 16:35, 27 October 2017

Contents

Objective

In this tutorial we will see how to setup a keil project to generate .bin file for LPC1768

Keil Setup Steps

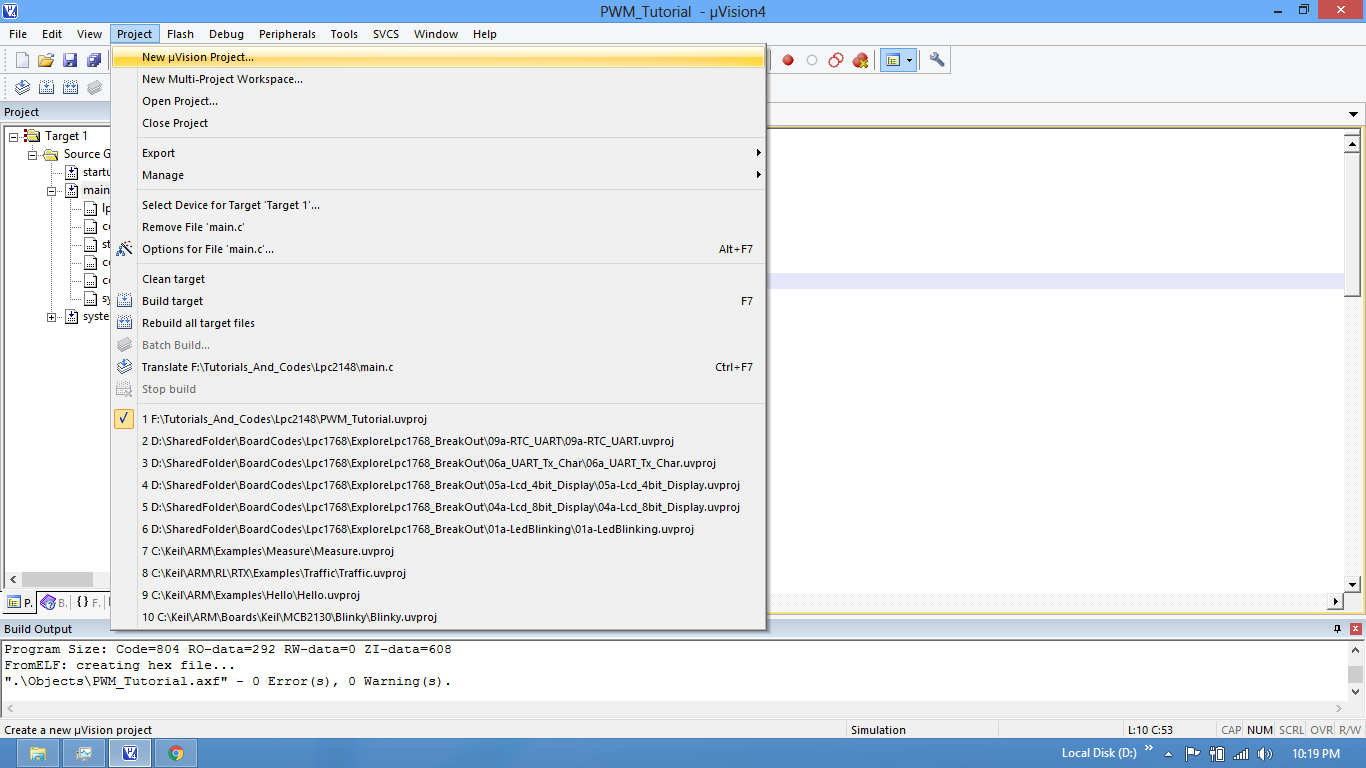

Step1: Open the Keil software and select the New Microvision project from Project Menu as shown below.

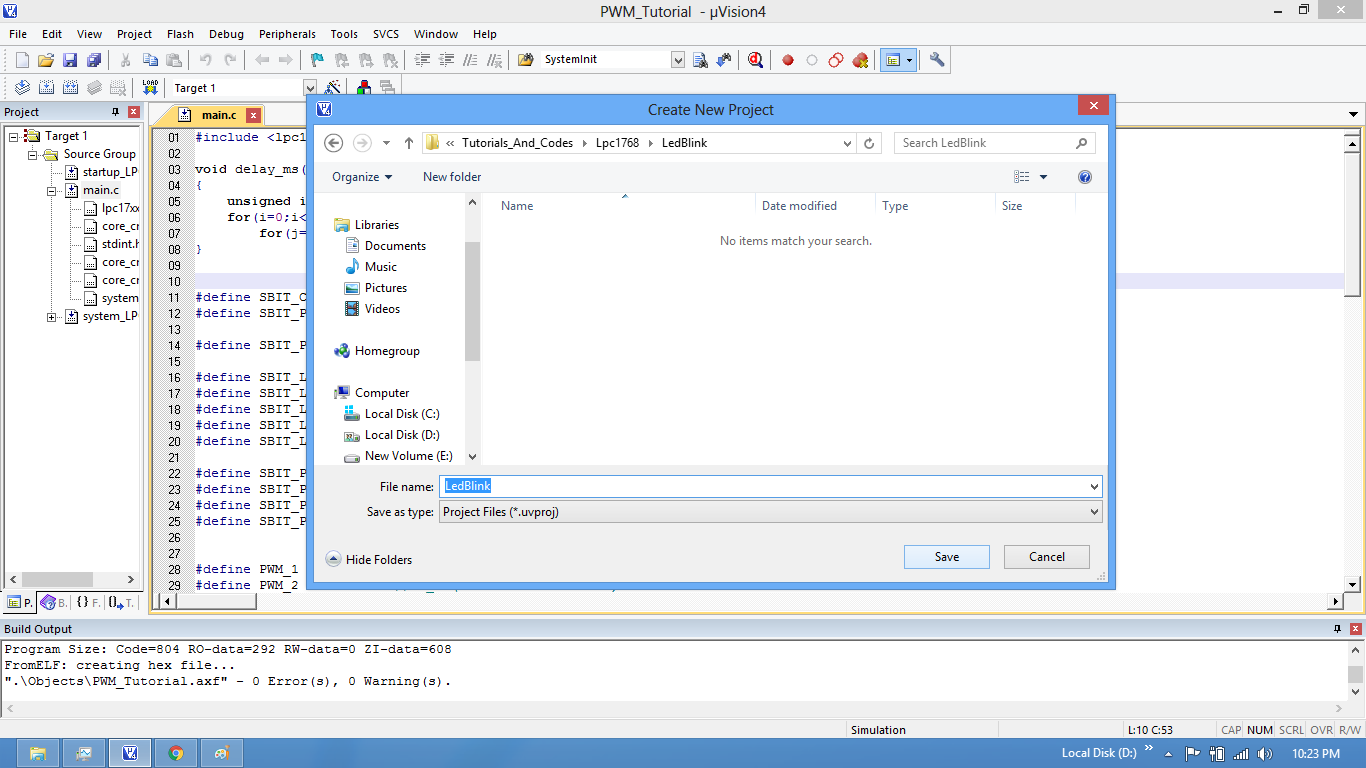

Step2: Browse to your project folder and provide the project name and click on save.

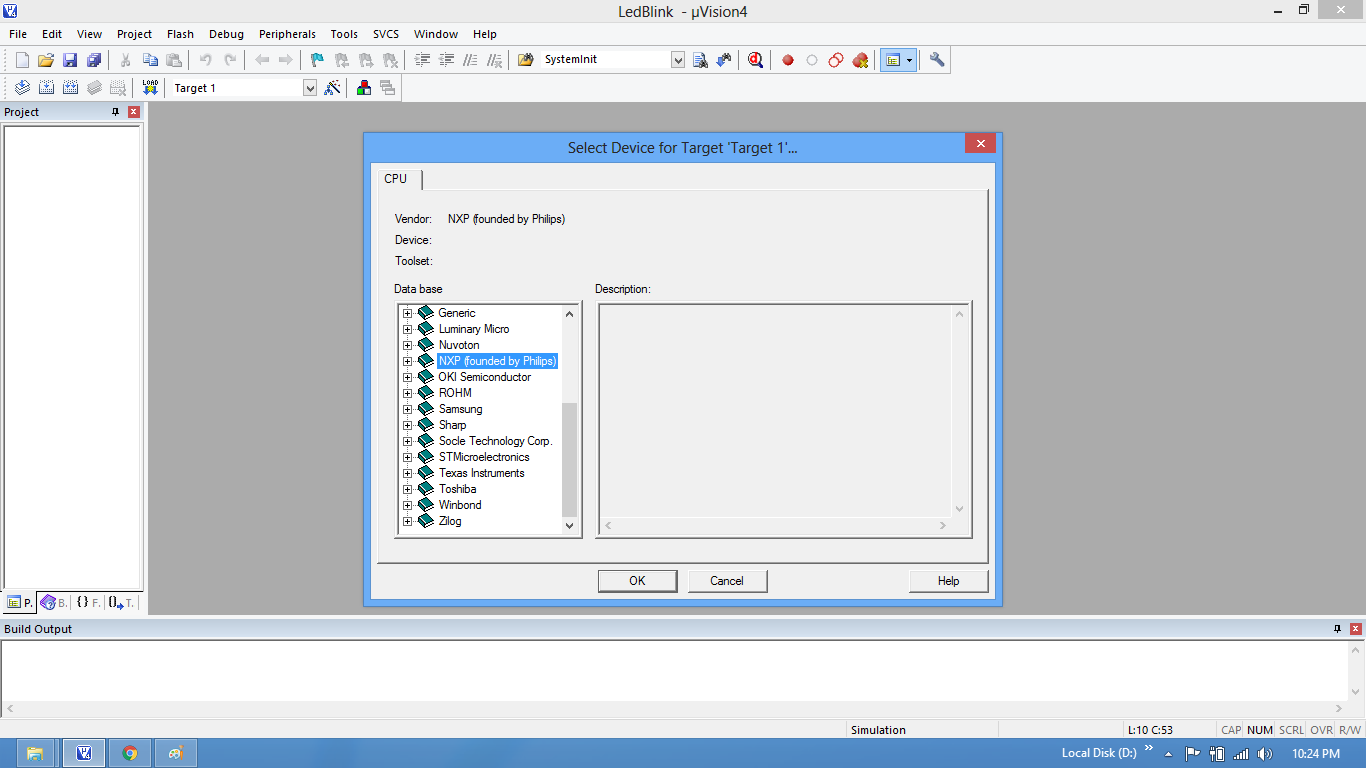

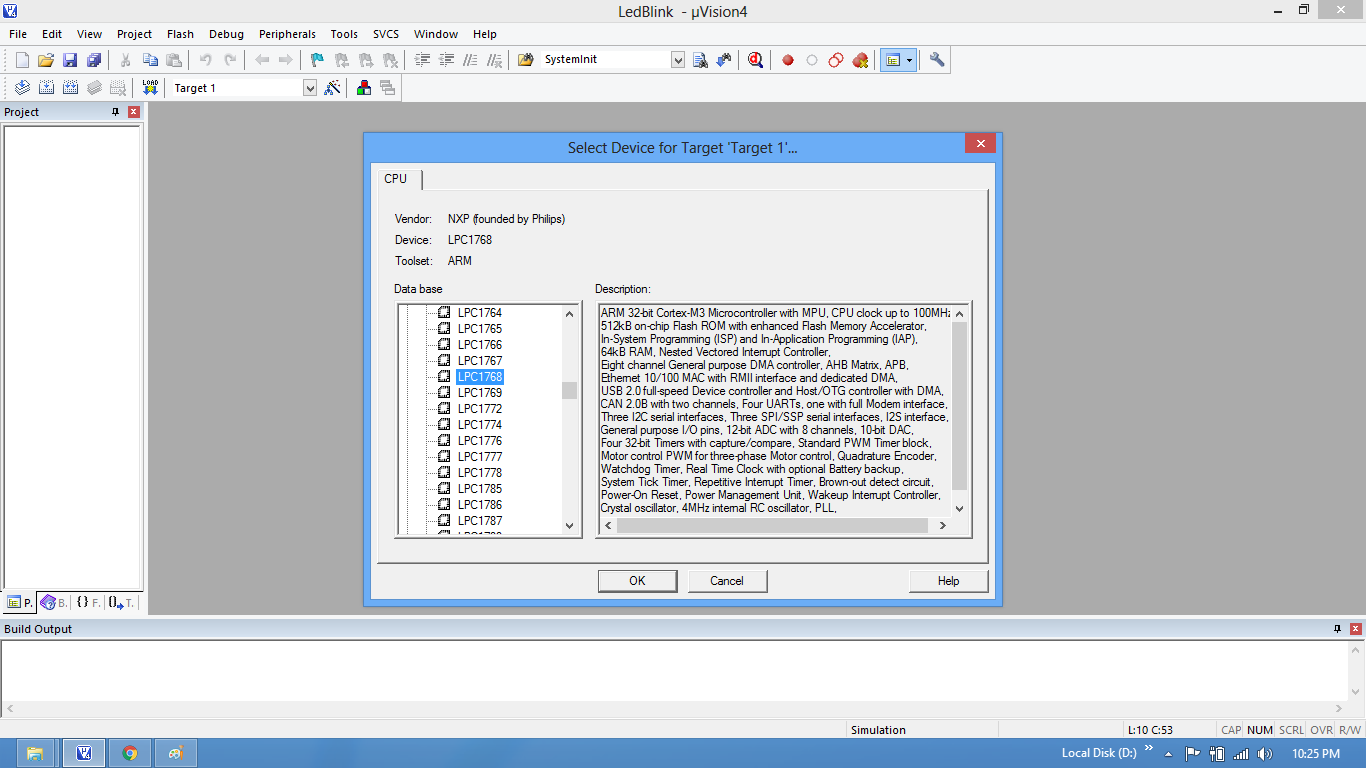

Step3: Once the project is saved a new pop up “Select Device for Target” opens, Select the controller(NXP:LPC1768) and click on OK.

Step4: Select the controller(NXP:LPC1768) and click on OK.

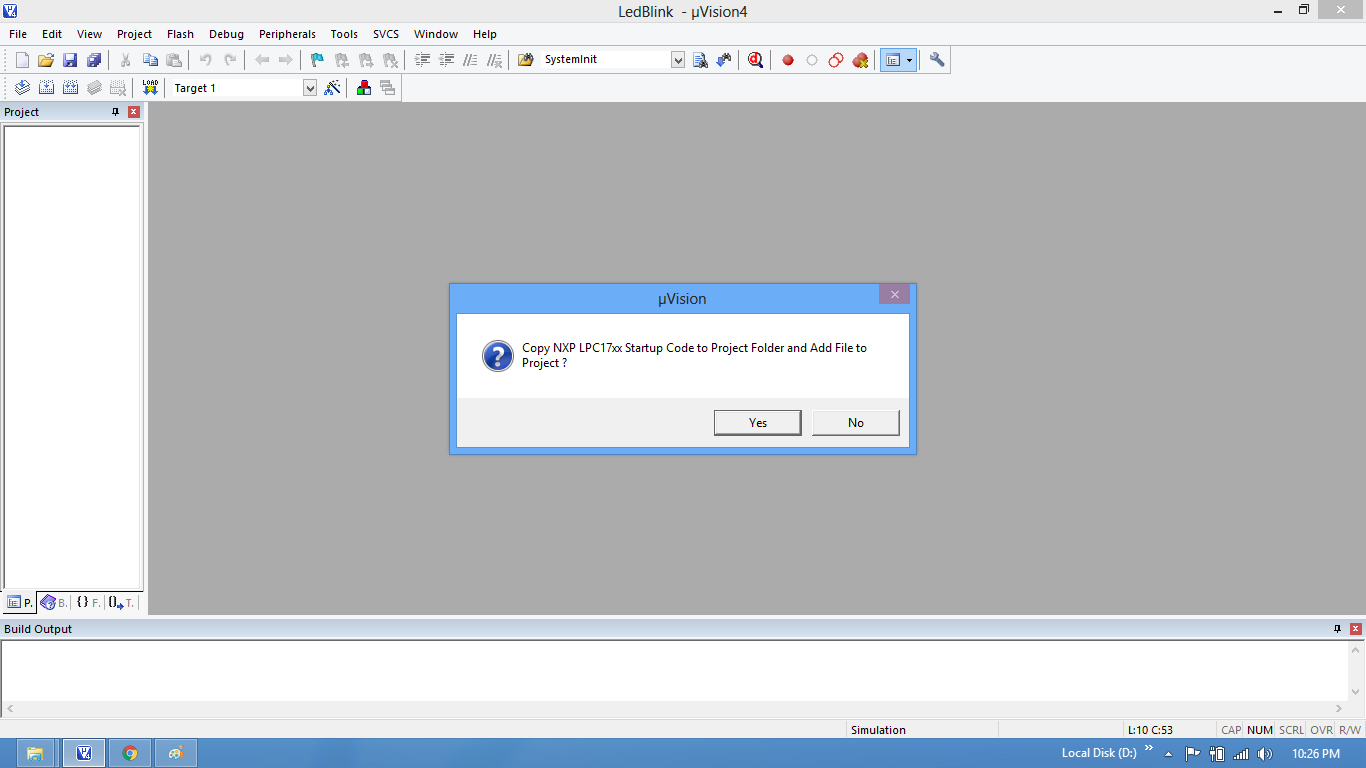

Step5: As LPC1768 needs the startup code, click on Yes option to include the LPC17xx Startup file.

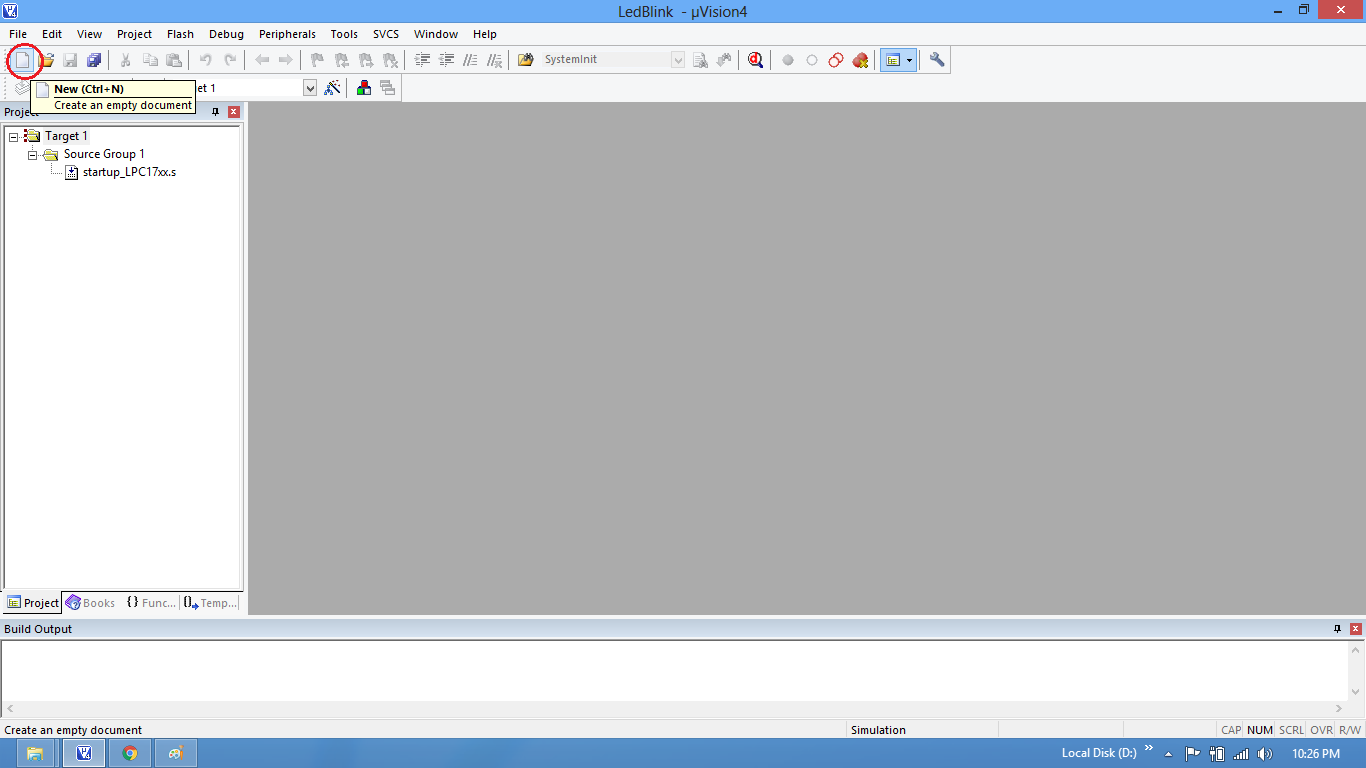

Step6: Create a new file to write the program.

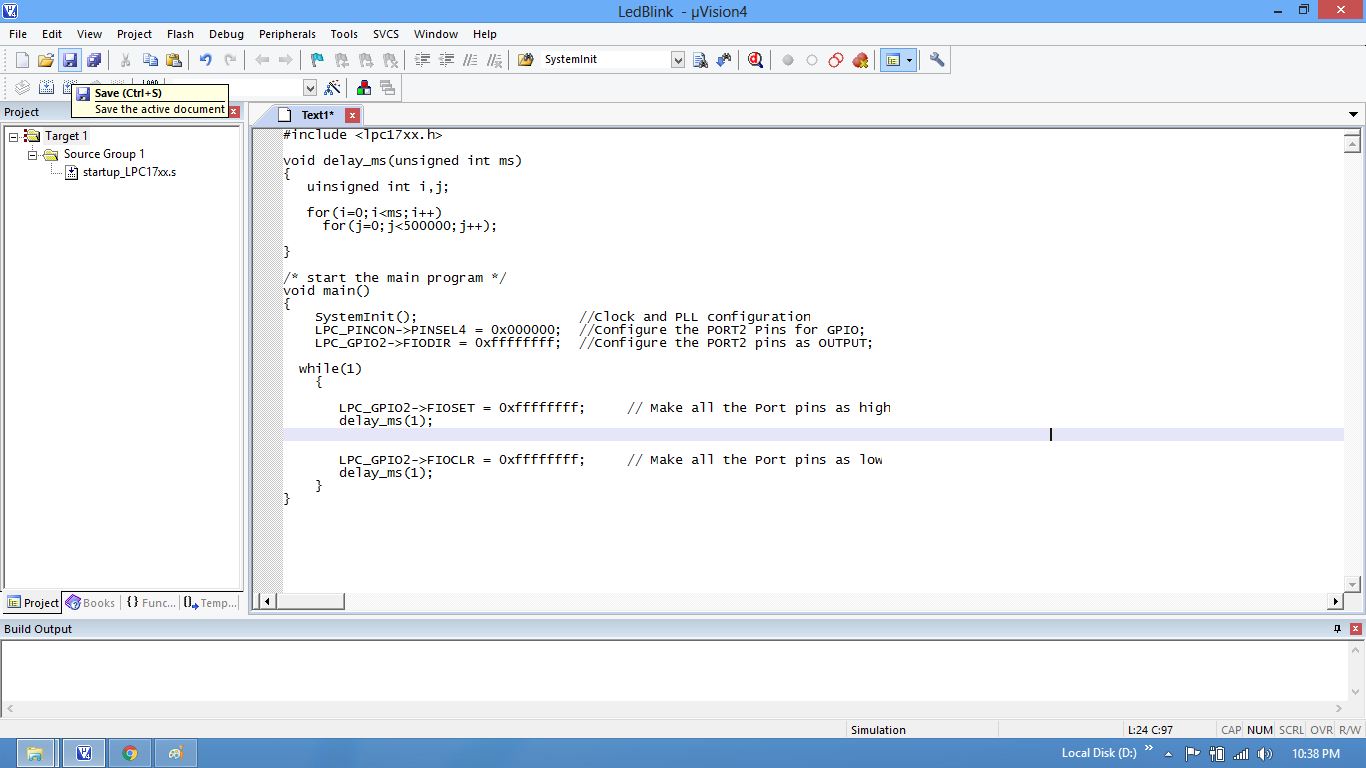

Step7: Type the code or Copy paste the below code snippet.

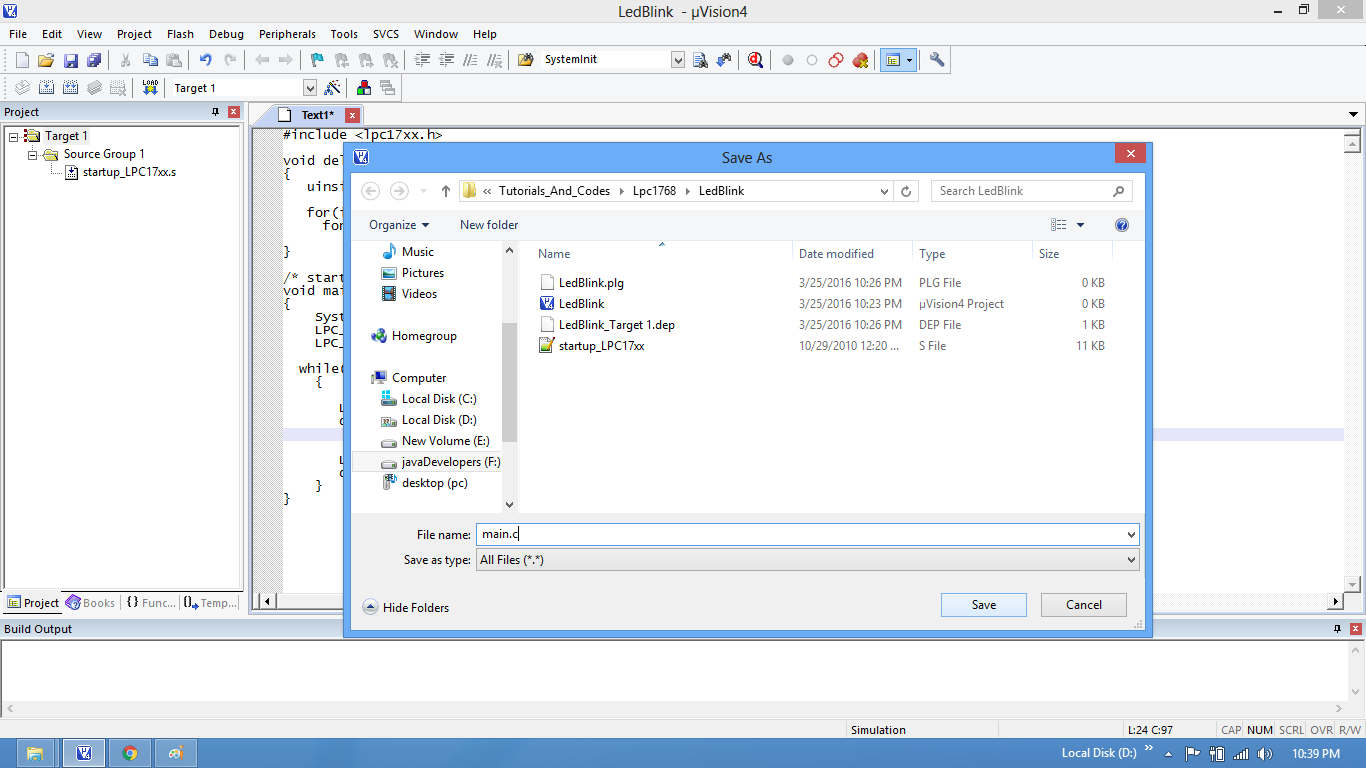

Step8: After typing the code save the file as main.c.

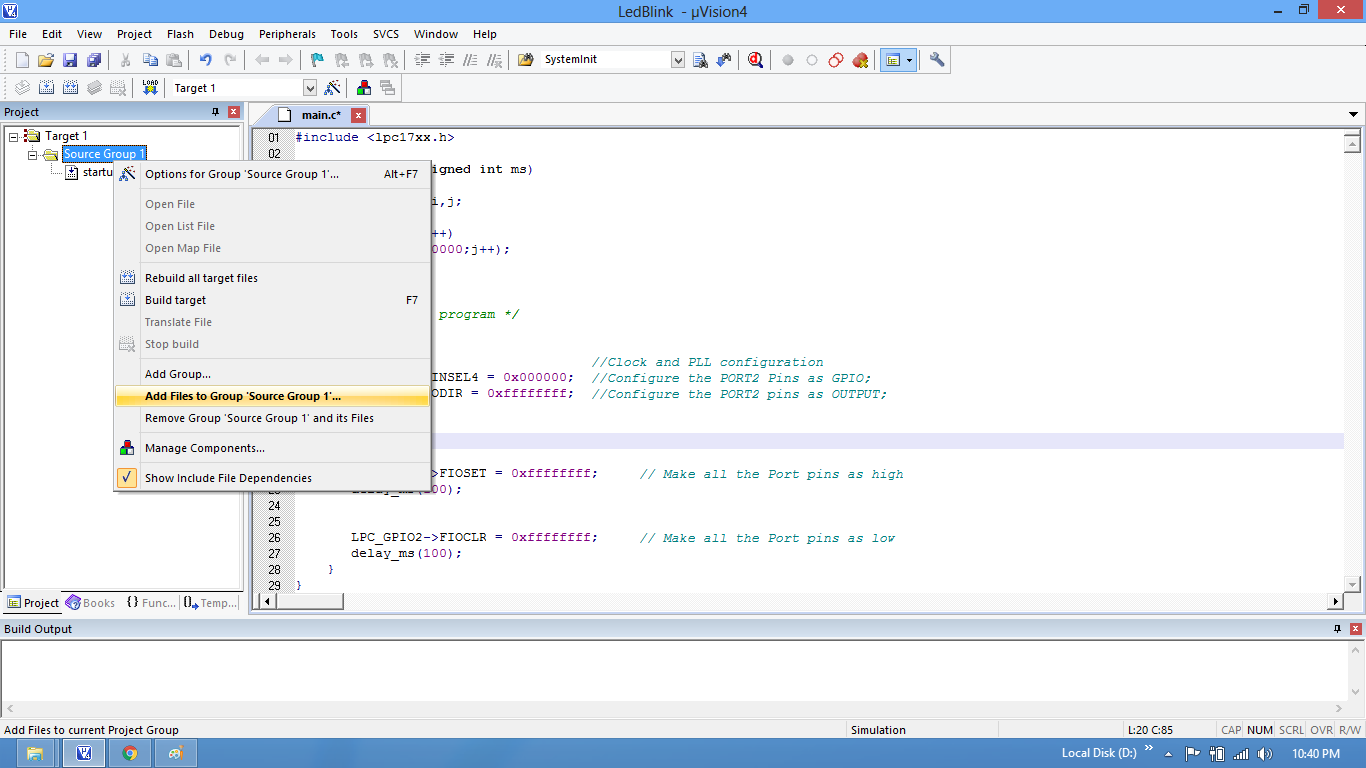

Step9: Add the recently saved file to the project.

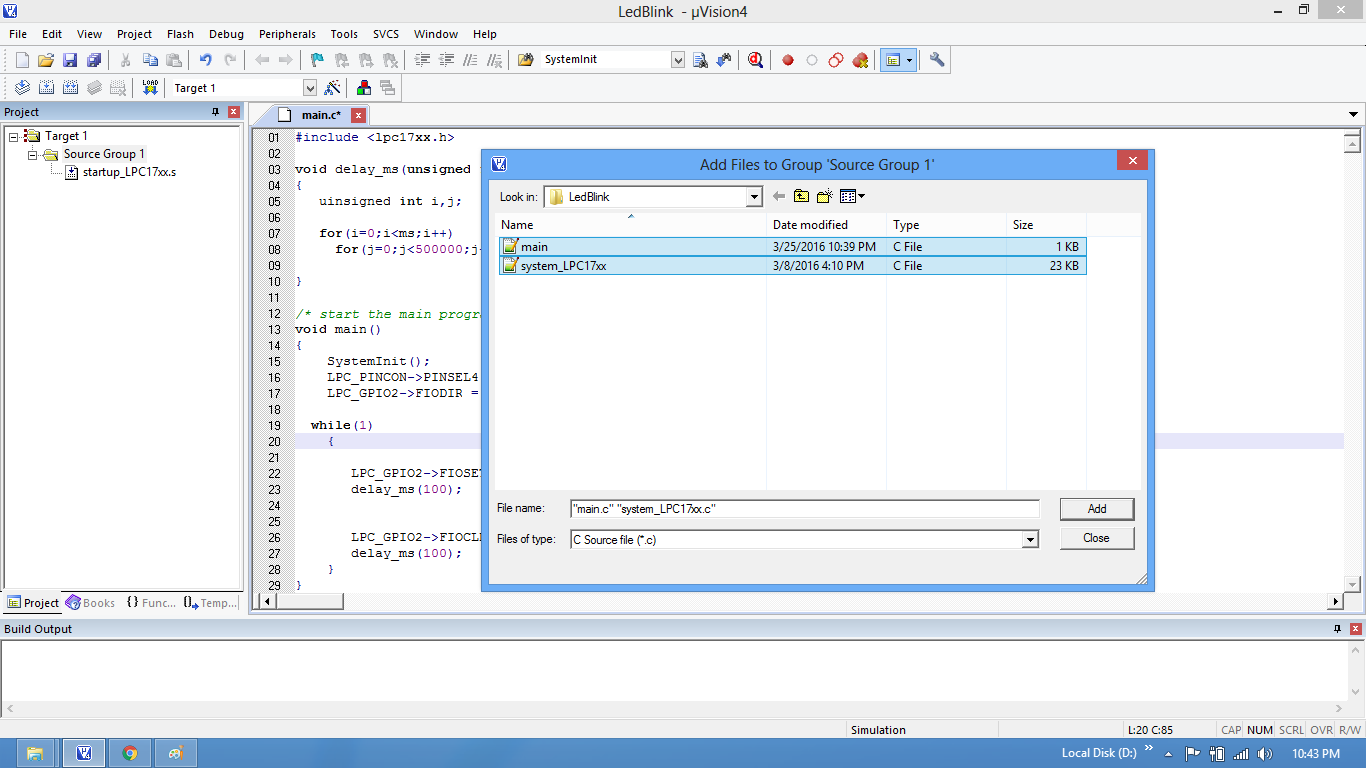

Step10: Add the main.c along with system_LPC17xx.c.

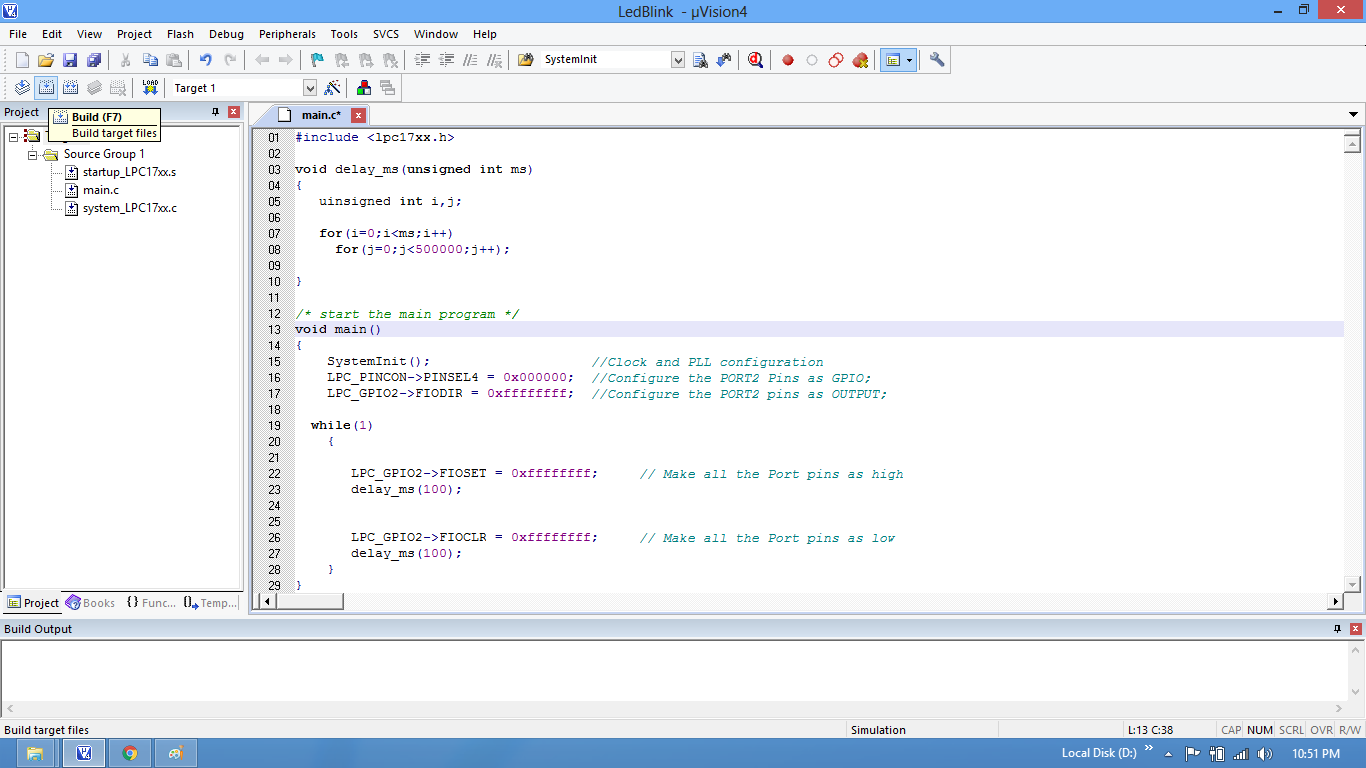

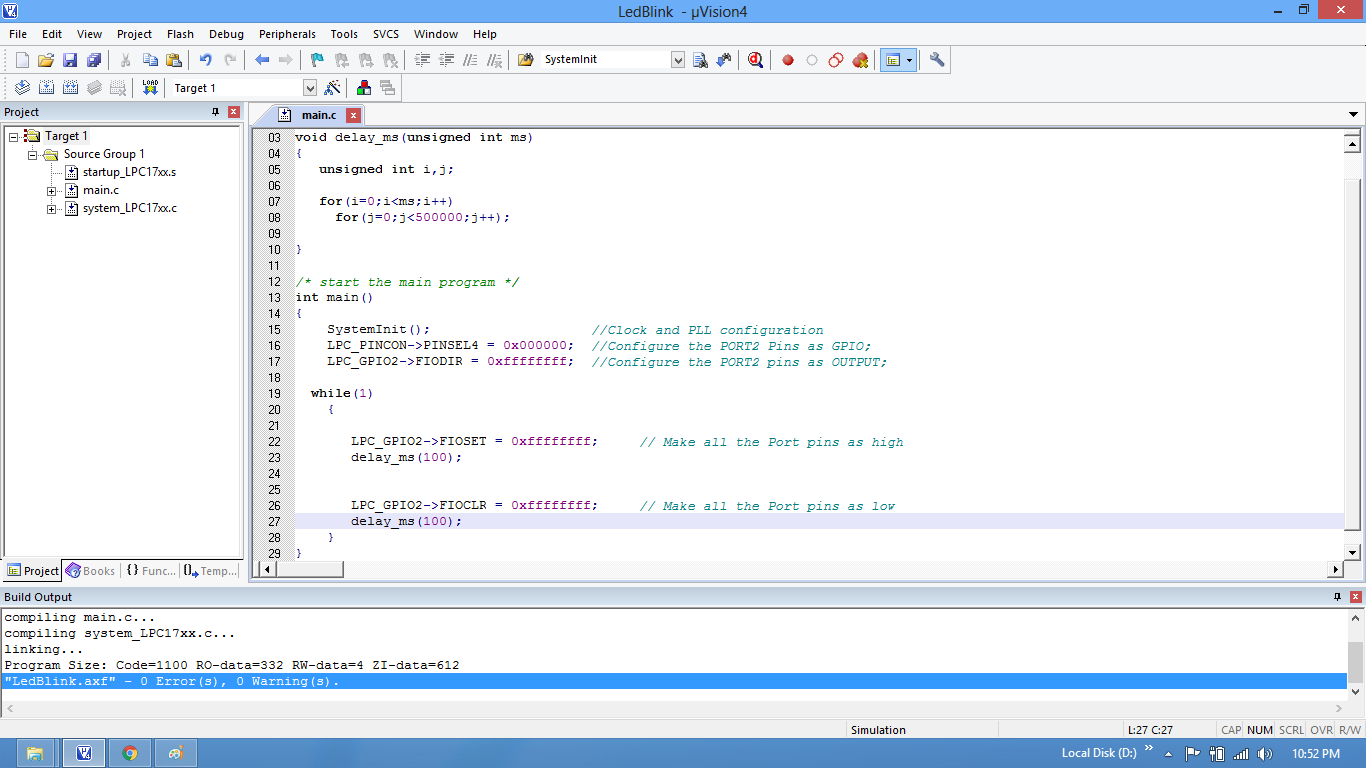

Step11: Build the project and fix the compiler errors/warnings if any.

Step12: Code is compiled with no errors. The .bin file is still not generated.

Setup Bin File Generation

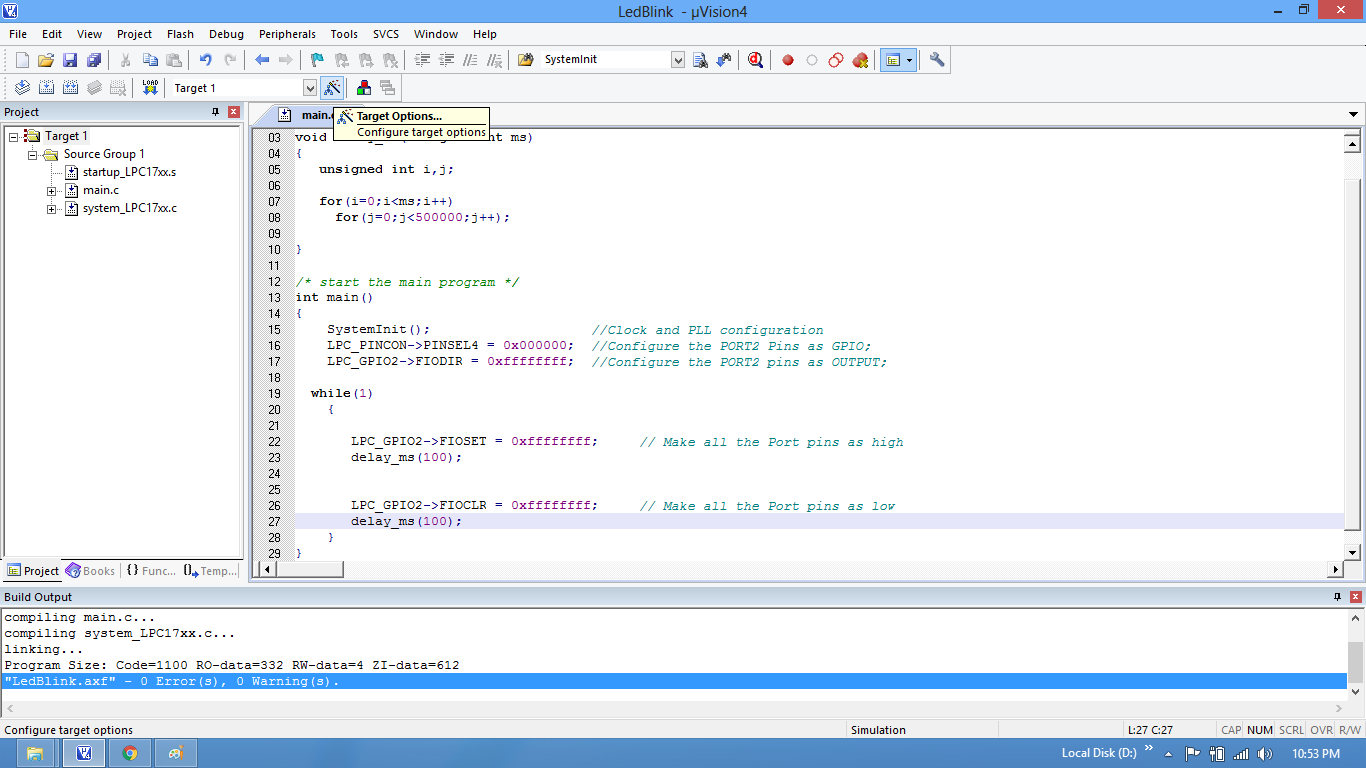

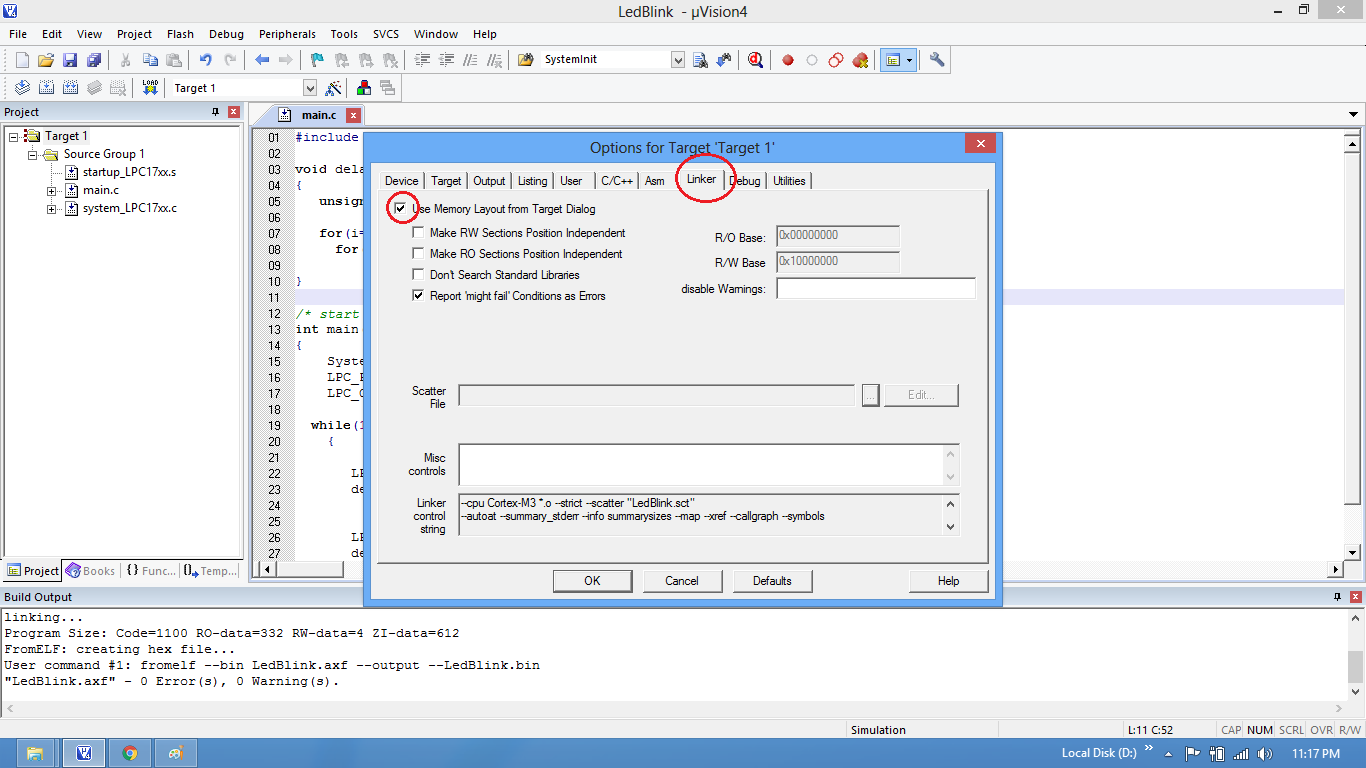

Step13: Click on Target Options to select the option for generating .bin file.

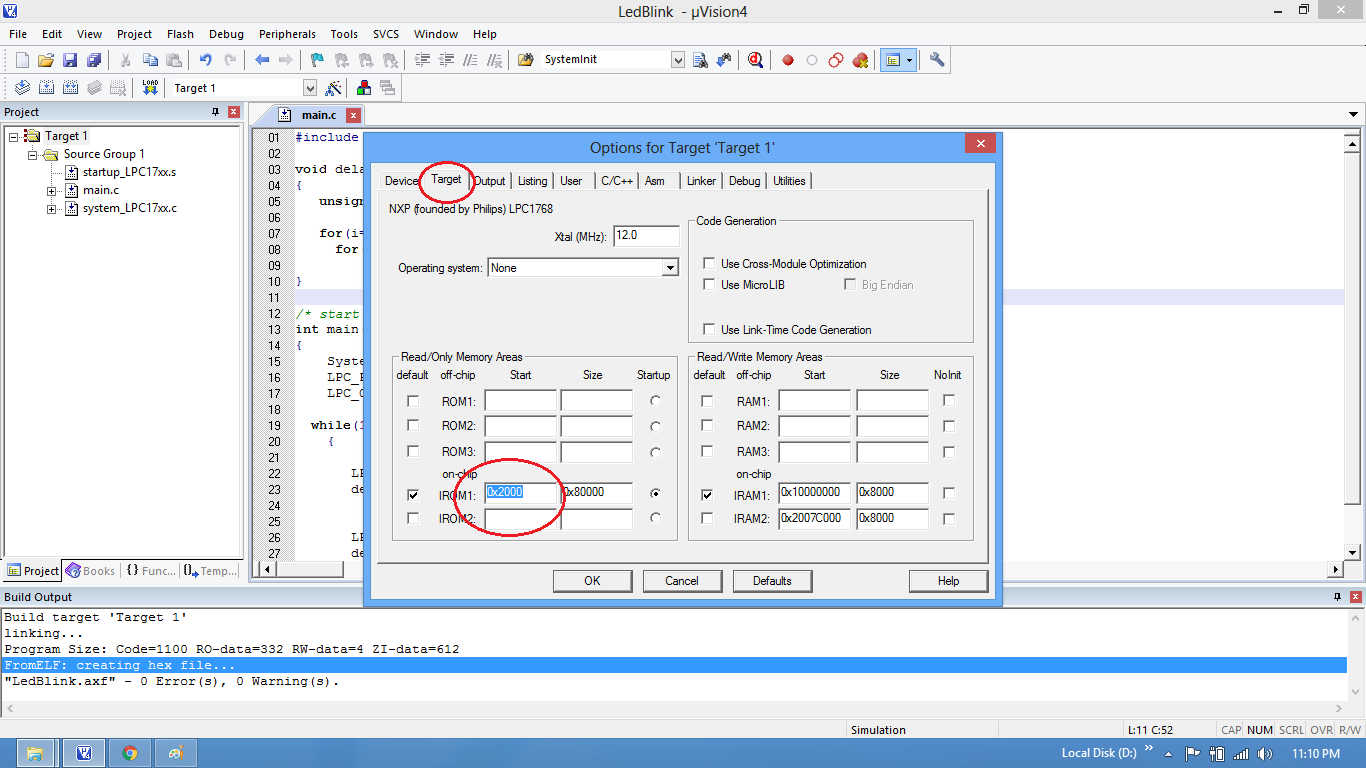

Step14: Set IROM1 start address as 0x2000. Bootloader will be stored from 0x0000-0x2000 so application should start from 0x2000

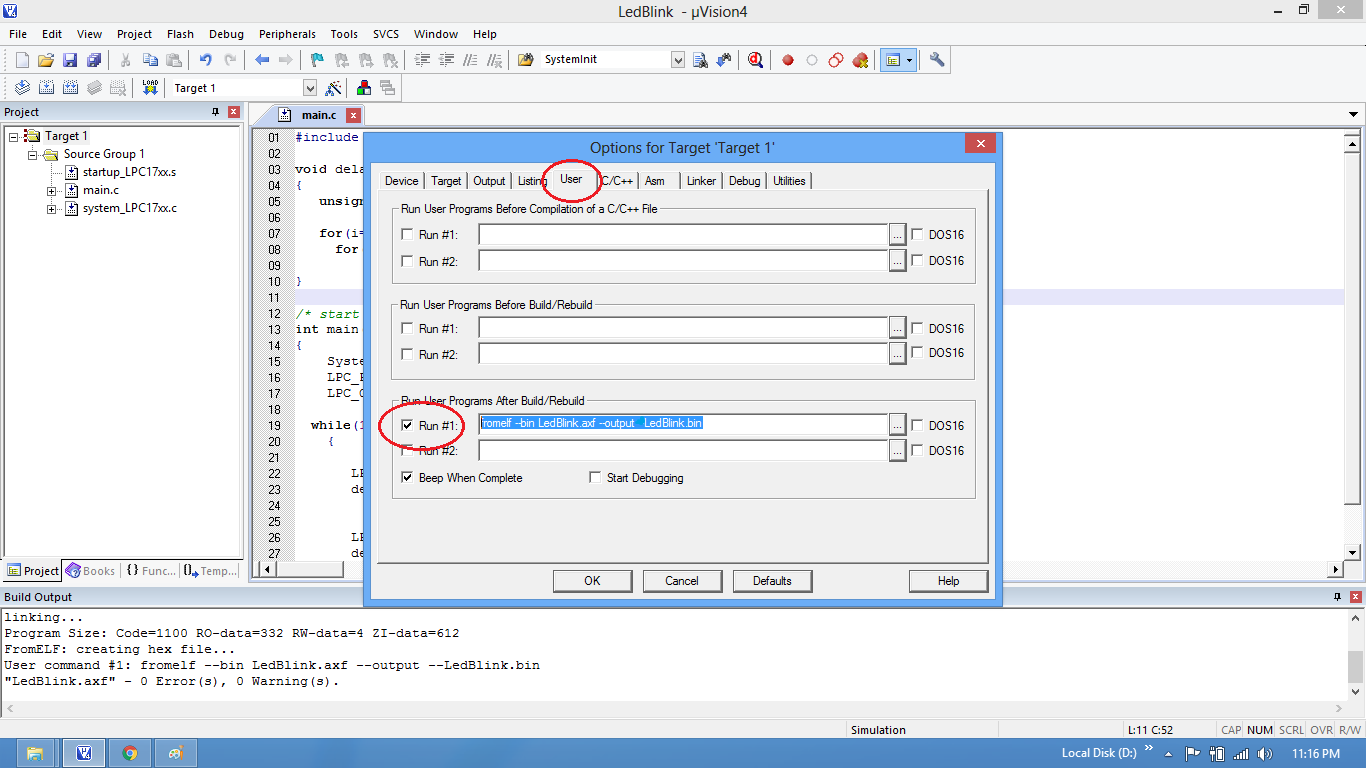

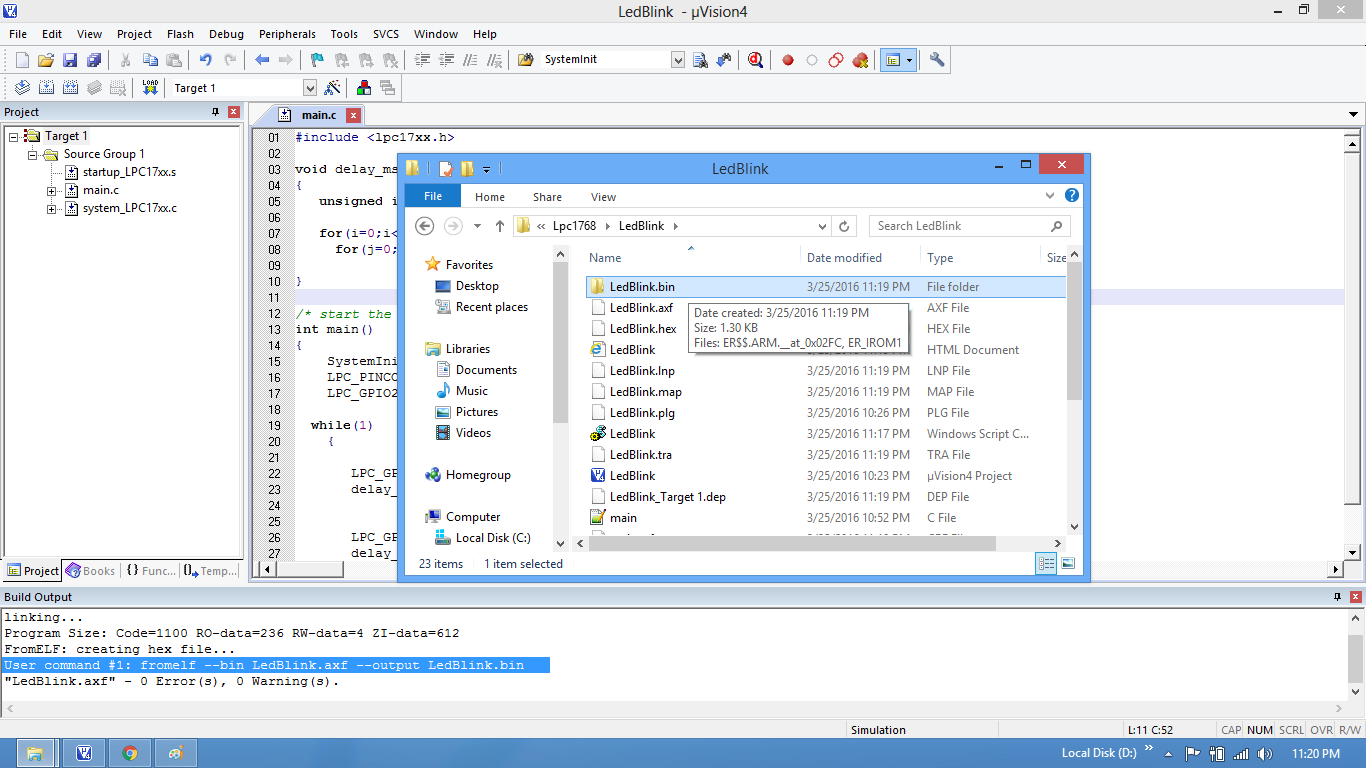

Step15: Write the command to generate the .bin file from .axf file

Command: fromelf --bin LedBlink.axf --output LedBlink.bin

Step16: Now enable the linker option to use the IROM1 address from target settings

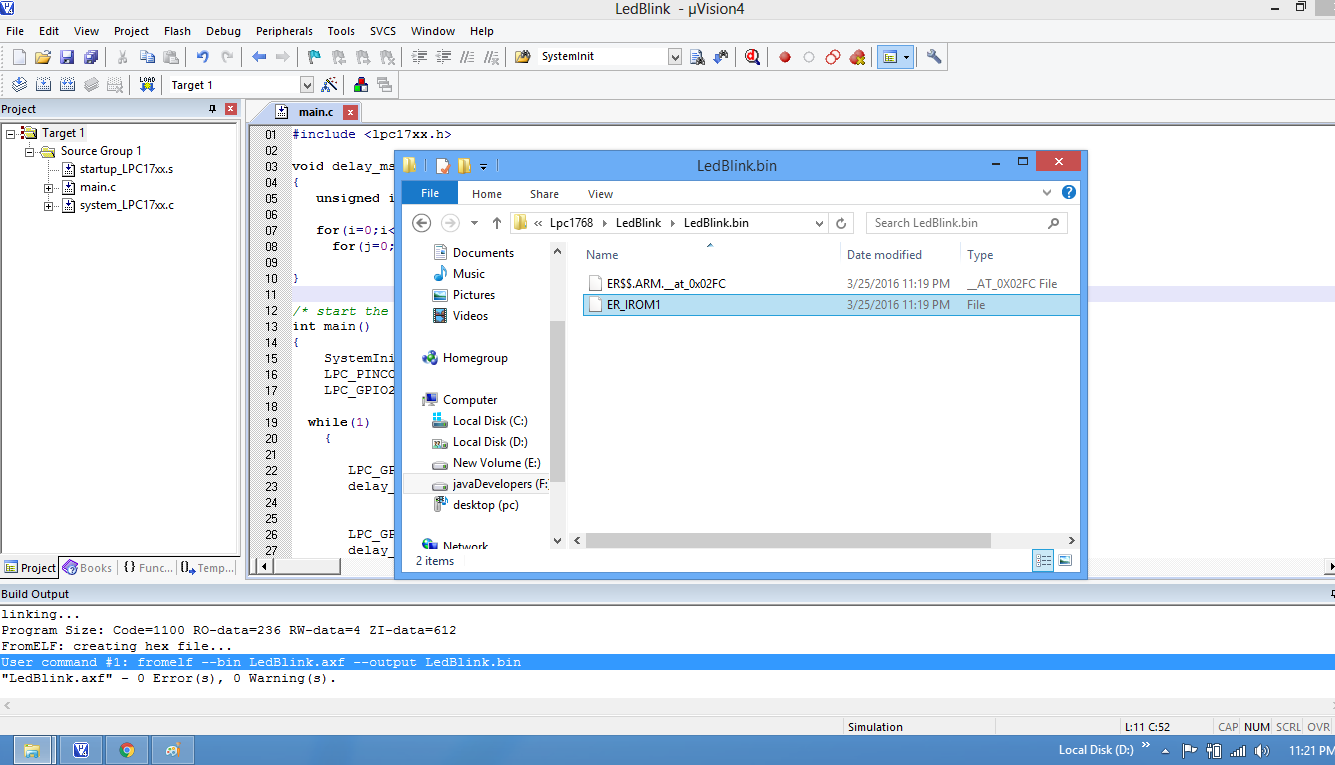

Step17: .Bin file is generated after a rebuild.

Step18: Check the project folder for the generated .Bin<ER_ROM1> file.

Uploading the Bin file

After generating the .bin file check this tutorial for Uploading Hex and Bin files..

Downloads

Download the complete project folder from the below link:

https://codeload.github.com/ExploreEmbedded/Explore-Cortex-M3-LPC1768-Stick-DVB-14001/zip/master

Have a opinion, suggestion , question or feedback about the article let it out here!