Difference between revisions of "A4.8051 Communication Protocols:UART, RS232"

m |

|||

| Line 1: | Line 1: | ||

[[Category:8051_tutorials]] | [[Category:8051_tutorials]] | ||

| − | + | In this tutorial, we are going to discuss the serial/UART communication of 8051. After understating the basics of 8051 UART module, We will see how to use the ExploreEmbedded libraries to communicate with any of the UART devices.<br><br> | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| + | [[File:0 UART main.gif]] | ||

| − | |||

| − | |||

| − | |||

| − | = | + | =UART Registers= |

| − | + | The below table shows the registers associated with 8051 UART.<br> | |

| − | + | {| class="table table-striped table-hover table-condensed table-bordered" | |

| − | + | |-class="info" | |

| − | + | !Register || Description | |

| − | The | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | {| class=" | + | |

|- | |- | ||

| − | + | |SCON|| Serial Control Register | |

|- | |- | ||

| − | | | + | |TCON|| Timer Control Register for Baud Rate Generator |

|- | |- | ||

| − | | | + | |TMOD|| Timer Mode Control for Baud Rate Generator |

|- | |- | ||

| − | | | + | |SBUFF||Serial Buffer holds the data to be transmitted and the data received |

|} | |} | ||

| + | <br><br> | ||

| − | + | =UART Register Configuration= | |

| − | + | Now lets see how to configure the individual registers for UART communication. | |

| − | + | {| class="table table-striped table-hover table-condensed table-bordered" | |

| − | + | |-class="info" | |

| − | + | |SCON | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | {| class=" | + | |

|- | |- | ||

| − | + | |7 || 6 || 5 || 4 || 3 || 2 || 1 || 0 | |

|- | |- | ||

| − | | | + | |SM0||SM1||SM2||REN||TB8||RB8||TI||RI |

|} | |} | ||

| − | + | <b>SM0,SM1</b> Serial port mode selection<br> | |

| − | + | {| class="table table-striped table-hover table-condensed table-bordered" | |

| − | + | |-class="info" | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | {| class=" | + | |

| − | |- | + | |

!SM0||SM1||Operation||Description||Baud Rate Source | !SM0||SM1||Operation||Description||Baud Rate Source | ||

|- | |- | ||

|0||0||Mode 0|| 8bit ShiftReg||1/12 the quartz frequency | |0||0||Mode 0|| 8bit ShiftReg||1/12 the quartz frequency | ||

| − | |- | + | |- |

|0||1||Mode 1|| 8 bit UART||Determined by the timer 1 | |0||1||Mode 1|| 8 bit UART||Determined by the timer 1 | ||

|- | |- | ||

| Line 82: | Line 45: | ||

|1||1||Mode 0|| 9 bit UART||Determined by the timer 1 | |1||1||Mode 0|| 9 bit UART||Determined by the timer 1 | ||

|} | |} | ||

| − | + | ||

| − | * | + | *<b>SM2 - Serial port mode 2 bit</b>, also known as multiprocessor communication enable bit. When set, it enables multiprocessor communication in mode 2 and 3, and eventually mode 1. It should be cleared in mode 0. |

*'''REN - Reception Enable bit''' enables serial reception when set. When cleared, serial reception is disabled. | *'''REN - Reception Enable bit''' enables serial reception when set. When cleared, serial reception is disabled. | ||

*'''TB8 - Transmitter bit 8'''. Since all registers are 8-bit wide, this bit solves the problem of transmitting the 9th bit in modes 2 and 3. It is set to transmit a logic 1 in the 9th bit. | *'''TB8 - Transmitter bit 8'''. Since all registers are 8-bit wide, this bit solves the problem of transmitting the 9th bit in modes 2 and 3. It is set to transmit a logic 1 in the 9th bit. | ||

*'''RB8''' - Receiver bit 8 or the 9th bit received in modes 2 and 3. Cleared by hardware if 9th bit received is a logic 0. Set by hardware if 9th bit received is a logic 1. | *'''RB8''' - Receiver bit 8 or the 9th bit received in modes 2 and 3. Cleared by hardware if 9th bit received is a logic 0. Set by hardware if 9th bit received is a logic 1. | ||

| − | *'''TI''' - Transmit Interrupt flag is automatically set at the moment the last bit of one byte is sent. It's a signal to the processor that the line is available for a new byte transmit. It must be cleared from within the software. | + | *'''TI''' - Transmit Interrupt flag is automatically set at the moment the last bit of one byte is sent. It's a signal to the processor that the line is available for a new byte to transmit. It must be cleared from within the software. |

| − | *'''RI''' - Receive Interrupt flag is automatically set upon one byte receive. It signals that byte is received and should be read quickly prior to being replaced by a new data. This bit is also cleared from within the software. | + | *'''RI''' - Receive Interrupt flag is automatically set upon one-byte receive. It signals that byte is received and should be read quickly prior to being replaced by a new data. This bit is also cleared from within the software. |

| − | |||

| − | |||

| − | |||

| − | |||

| − | + | {| class="table table-striped table-hover table-condensed table-bordered" | |

| − | + | |-class="info" | |

| − | + | |RCSTA | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | {| class=" | + | |

|- | |- | ||

| − | + | |7 || 6 || 5 || 4 || 3 || 2 || 1 || 0 | |

|- | |- | ||

| − | | | + | |SPEN || RX9 || SREN || CREN || ADDEN || FERR || OERR || RX9D |

| − | | | + | |

| − | | | + | |

| − | | | + | |

| − | | | + | |

| − | | | + | |

| − | | | + | |

| − | + | ||

| − | + | ||

|} | |} | ||

| − | + | <b>SPEN:</b> Serial Port Enable bit<br> | |

| − | + | 1 = Serial port enabled (configures RC7/RX/DT and RC6/TX/CK pins as serial port pins)<br> | |

| − | + | 0 = Serial port disabled | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | = | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | <br | + | |

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | ||

| − | + | <b>RX9:</b> 9-bit Receive Enable bit<br> | |

| + | 1 = Selects 9-bit reception<br> | ||

| + | 0 = Selects 8-bit reception | ||

| + | <b>SREN:</b> Single Receive Enable bit<br> | ||

| + | Asynchronous mode:Don’t care. | ||

| − | + | <b>CREN:</b> Continuous Receive Enable bit<br> | |

| + | Asynchronous mode:<br> | ||

| + | 1 = Enables continuous receive<br> | ||

| + | 0 = Disables continuous receive | ||

| − | = | + | <b>ADDEN:</b> Address Detect Enable bit<br> |

| − | + | Asynchronous mode 9-bit (RX9 = 1):<br> | |

| + | 1 = Enables address detection, enables interrupt and load of the receive buffer when RSR is set<br> | ||

| + | 0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit | ||

| − | + | <b>FERR:</b> Framing Error bit<br> | |

| + | 1 = Framing error (can be updated by reading RCREG register and receive next valid byte)<br> | ||

| + | 0 = No framing error | ||

| + | <b>OERR:</b> Overrun Error bit<br> | ||

| + | 1 = Overrun error (can be cleared by clearing bit CREN)<br> | ||

| + | 0 = No overrun error | ||

| + | <b>RX9D:</b> 9th bit of Received Data (can be parity bit but must be calculated by user firmware) | ||

| + | <br><br> | ||

| + | =Baud Rate Calculation= | ||

| + | The main criteria for UART communication is its baud rate. Both the devices Rx/Tx should be set to same baud rate for successful communication.<br> | ||

| + | This can be achieved by SPBRG register. SPBRG is a 8-bit register which controls the baud rate generation.<br> | ||

| + | Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the below formula. | ||

| + | *BRGH = 1 High Speed | ||

| + | $$SPBRG = (Fosc / (16 * BaudRate)) - 1$$ | ||

| + | *BRGH = 0 Low Speed | ||

| + | $$SPBRG = (Fosc / (64 * Baud rate)) - 1$$ | ||

| + | It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks. | ||

| + | This is because the FOSC/(16 (X + 1)) equation can reduce the baud rate error in some cases. Below table shows the list of standard BaudRates and the SPBRG values. | ||

| + | [[FILE:Pic16f877a_BaudRates.png]] | ||

| + | =Steps To Send Char= | ||

| + | #Wait till the previous char is transmitted. TXIF will be set when the TXREG is empty. | ||

| + | #Clear the TXIF for next cycle. | ||

| + | #Load the new char to be transmitted into THR.<br> | ||

| + | <html> | ||

| + | <script src="https://gist.github.com/SaheblalBagwan/ef0f2b16bc6eb398a8e7a2d272bd74dc.js"></script> | ||

| + | </html> | ||

| + | <br><br> | ||

| + | =Steps To Receive Char= | ||

| + | #Wait till the Data is received. RCIF will be set once the data is received in RCREG register. | ||

| + | #Clear the receiver flag(RCIF) for next cycle. | ||

| + | #Copy/Read the received data from RCREG register.<br> | ||

| + | <html> | ||

| + | <script src="https://gist.github.com/SaheblalBagwan/f47ebf0daaffe565a1d64aa6daea8bab.js"></script> | ||

| + | </html> | ||

| + | <br><br> | ||

| + | =Code= | ||

| + | Below is the sample code to Transmit and receive the chars at 9600 baudrate with 20Mhz clock. | ||

| + | <html> | ||

| + | <script src="https://gist.github.com/SaheblalBagwan/28efb0ab8aa0523bd1fcaf40abca3d3b.js"></script> | ||

| + | </html> | ||

| + | =Using ExploreEmbedded Libraries= | ||

| + | In the above tutorial we discussed how to configure and use the inbuilt Pic16f877a UART.<br> | ||

| + | Now we will see how to use the ExploreEmbededd UART library.<br> | ||

| + | For this you have to include the uart.c/uart.h files and associated gpio/stdutils files.<br> | ||

| + | *Note:Refer the uart.h file for more info. | ||

| + | <html> | ||

| + | <script src="https://gist.github.com/sharanago/12a15188d6143edfa7ba6408d6c1da02.js"></script> | ||

| + | </html> | ||

| + | [[File:Pic16f877a uart.PNG]]<br><br> | ||

| − | + | =Downloads= | |

| − | + | Download the complete project folder from the below link:<br> | |

| + | [https://github.com/ExploreEmbedded/Pic16f877a_ExploreUltraPicDevKit/archive/master.zip Hardware design Files and Code Library] | ||

| − | Have a opinion, suggestion, | + | Have a opinion, suggestion , question or feedback about the article let it out here! |

{{DISQUS}} | {{DISQUS}} | ||

Revision as of 17:53, 20 August 2016

In this tutorial, we are going to discuss the serial/UART communication of 8051. After understating the basics of 8051 UART module, We will see how to use the ExploreEmbedded libraries to communicate with any of the UART devices.

Contents

UART Registers

The below table shows the registers associated with 8051 UART.

| Register | Description |

|---|---|

| SCON | Serial Control Register |

| TCON | Timer Control Register for Baud Rate Generator |

| TMOD | Timer Mode Control for Baud Rate Generator |

| SBUFF | Serial Buffer holds the data to be transmitted and the data received |

UART Register Configuration

Now lets see how to configure the individual registers for UART communication.

| SCON | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SM0 | SM1 | SM2 | REN | TB8 | RB8 | TI | RI |

SM0,SM1 Serial port mode selection

| SM0 | SM1 | Operation | Description | Baud Rate Source |

|---|---|---|---|---|

| 0 | 0 | Mode 0 | 8bit ShiftReg | 1/12 the quartz frequency |

| 0 | 1 | Mode 1 | 8 bit UART | Determined by the timer 1 |

| 1 | 0 | Mode 2 | 9 bit UART | 1/32 the quartz frequency |

| 1 | 1 | Mode 0 | 9 bit UART | Determined by the timer 1 |

- SM2 - Serial port mode 2 bit, also known as multiprocessor communication enable bit. When set, it enables multiprocessor communication in mode 2 and 3, and eventually mode 1. It should be cleared in mode 0.

- REN - Reception Enable bit enables serial reception when set. When cleared, serial reception is disabled.

- TB8 - Transmitter bit 8. Since all registers are 8-bit wide, this bit solves the problem of transmitting the 9th bit in modes 2 and 3. It is set to transmit a logic 1 in the 9th bit.

- RB8 - Receiver bit 8 or the 9th bit received in modes 2 and 3. Cleared by hardware if 9th bit received is a logic 0. Set by hardware if 9th bit received is a logic 1.

- TI - Transmit Interrupt flag is automatically set at the moment the last bit of one byte is sent. It's a signal to the processor that the line is available for a new byte to transmit. It must be cleared from within the software.

- RI - Receive Interrupt flag is automatically set upon one-byte receive. It signals that byte is received and should be read quickly prior to being replaced by a new data. This bit is also cleared from within the software.

| RCSTA | |||||||

| 7 | 6 | 5 | 4 | 3 | 2 | 1 | 0 |

| SPEN | RX9 | SREN | CREN | ADDEN | FERR | OERR | RX9D |

SPEN: Serial Port Enable bit

1 = Serial port enabled (configures RC7/RX/DT and RC6/TX/CK pins as serial port pins)

0 = Serial port disabled

RX9: 9-bit Receive Enable bit

1 = Selects 9-bit reception

0 = Selects 8-bit reception

SREN: Single Receive Enable bit

Asynchronous mode:Don’t care.

CREN: Continuous Receive Enable bit

Asynchronous mode:

1 = Enables continuous receive

0 = Disables continuous receive

ADDEN: Address Detect Enable bit

Asynchronous mode 9-bit (RX9 = 1):

1 = Enables address detection, enables interrupt and load of the receive buffer when RSR is set

0 = Disables address detection, all bytes are received and ninth bit can be used as parity bit

FERR: Framing Error bit

1 = Framing error (can be updated by reading RCREG register and receive next valid byte)

0 = No framing error

OERR: Overrun Error bit

1 = Overrun error (can be cleared by clearing bit CREN)

0 = No overrun error

RX9D: 9th bit of Received Data (can be parity bit but must be calculated by user firmware)

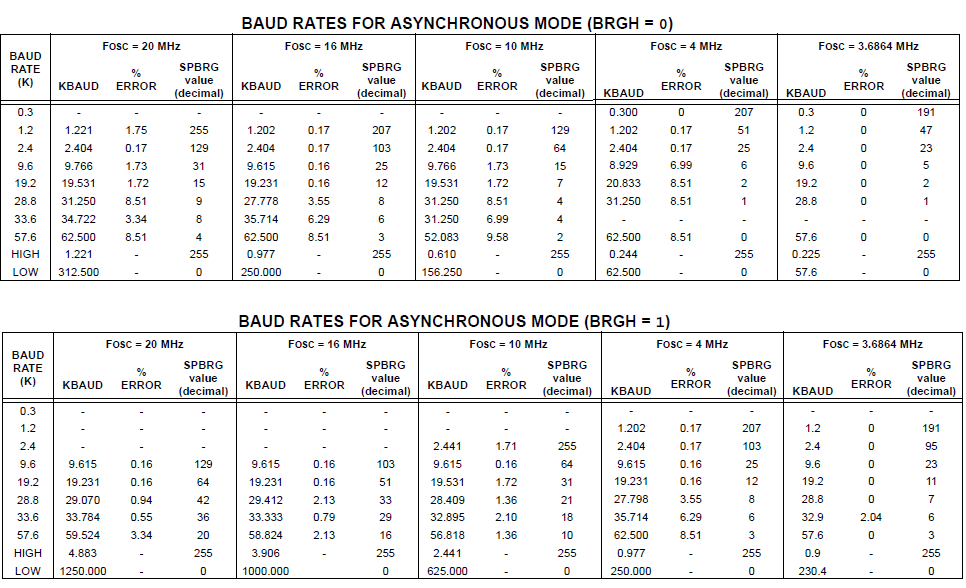

Baud Rate Calculation

The main criteria for UART communication is its baud rate. Both the devices Rx/Tx should be set to same baud rate for successful communication.

This can be achieved by SPBRG register. SPBRG is a 8-bit register which controls the baud rate generation.

Given the desired baud rate and FOSC, the nearest integer value for the SPBRG register can be calculated using the below formula.

- BRGH = 1 High Speed

$$SPBRG = (Fosc / (16 * BaudRate)) - 1$$

- BRGH = 0 Low Speed

$$SPBRG = (Fosc / (64 * Baud rate)) - 1$$

It may be advantageous to use the high baud rate (BRGH = 1) even for slower baud clocks.

This is because the FOSC/(16 (X + 1)) equation can reduce the baud rate error in some cases. Below table shows the list of standard BaudRates and the SPBRG values.

Steps To Send Char

- Wait till the previous char is transmitted. TXIF will be set when the TXREG is empty.

- Clear the TXIF for next cycle.

- Load the new char to be transmitted into THR.

Steps To Receive Char

- Wait till the Data is received. RCIF will be set once the data is received in RCREG register.

- Clear the receiver flag(RCIF) for next cycle.

- Copy/Read the received data from RCREG register.

Code

Below is the sample code to Transmit and receive the chars at 9600 baudrate with 20Mhz clock.

Using ExploreEmbedded Libraries

In the above tutorial we discussed how to configure and use the inbuilt Pic16f877a UART.

Now we will see how to use the ExploreEmbededd UART library.

For this you have to include the uart.c/uart.h files and associated gpio/stdutils files.

- Note:Refer the uart.h file for more info.

Downloads

Download the complete project folder from the below link:

Hardware design Files and Code Library

Have a opinion, suggestion , question or feedback about the article let it out here!