Overview of ESP32 features. What do they practically mean? (Redirected from Overview of ESP32: Features that matter the most!)

You should have heard enough about the new Chip! From the specifications looks like, this is THE chip of the future, for anything connected that you want to build. Instead of using a microcontroller and add-on WiFi, Bluetooth modules for building connected things , this is the only chip you might want to use. Sounds great? But wait, this brings in a lot of programming complexity. So in this tutorial, I will run through the specifications of the chip from the perspective of practical usefulness. The things that you need to know before you start out and the features that really matter!

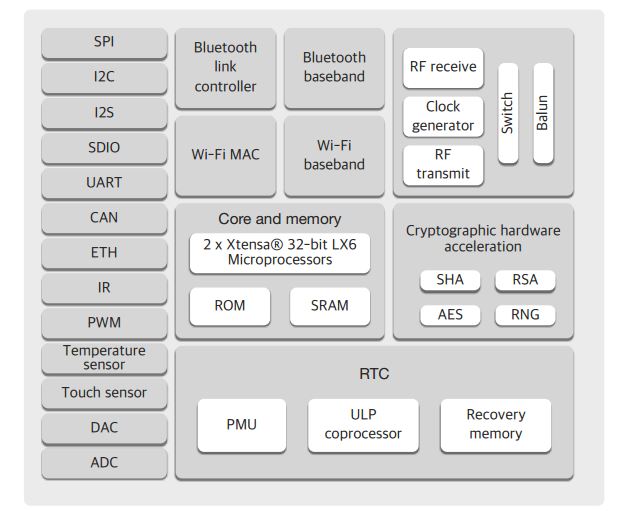

The block diagram below shows all that is in there! We will look at each of these blocks and see what they mean when using ESP32 in your project/product.

Contents

The Dual Core Processor

Do away with the external micro-controller/Arduino when building connected things....

The predecessor of ESP32, the ESP8266 has a builtin processor. However due to multitasking involved in updating the WiFi stack, most of the applications use a separate micro-controller for data processing, interfacing sensors and digital Input Output. With the ESP32 you may not want to use an additional micro-controller. ESP32 has Xtensa® Dual-Core 32-bit LX6 microprocessors, which runs up to 600 DMIPS. The ESP32 will run on breakout boards and modules from 160Mhz upto 240MHz . That is very good speed for anything that requires a microcontroller with connectivity options.

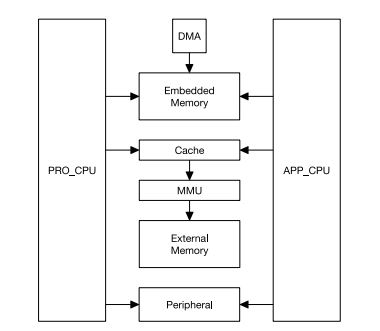

The two cores are named Protocol CPU (PRO_CPU) and Application CPU (APP_CPU). That basically means the PRO_CPU processor handles the WiFi, Bluetooth and other internal peripherals like SPI, I2C, ADC etc. The APP_CPU is left out for the application code. This differentiation is done in the Espressif Internet Development Framework (ESP-IDF). ESP-IDF is the official software development framework for the chip. Arduino and other implementations for the development will be based on ESP-IDF.

ESP-IDF uses freeRTOS for switching between the processors and data exchange between them. We have done numerous tutorials on freeRTOS and with all the bare-metal programming tutorials for ESP32 we will try and cover this aspect in detail. Although the feature set is great at the price at which the chip is being sold, the complexity is enormous. For the chip to get widely adopted, it will require huge efforts from Espressif as well as the community.

Internal Memory

The processors have closely tied internal memory for the following usage:

- 448 KBytes ROM for booting and core functions.

- 520 KBytes on-chip SRAM for data and instruction.

- 8 KBytes SRAM in RTC, which is called RTC SLOW Memory and can be accessed by the co-processor

- during the Deep-sleep mode.

- 8 KBytes SRAM in RTC, which is called RTC FAST Memory and can be used for data storage; it is accessed

- by the main CPU during RTC Boot from the Deep-sleep mode.

- 1 Kbit of EFUSE, of which 256 bits are used for the system (MAC address and chip configuration) and the remaining 768 bits are reserved for customer applications, including Flash-Encryption and Chip-ID

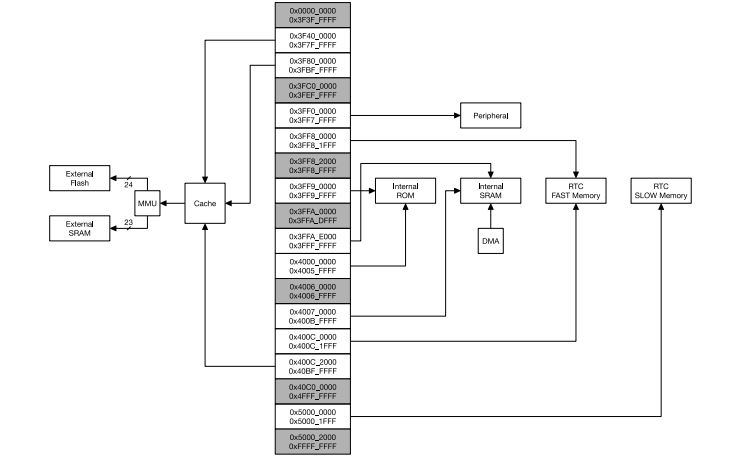

External Flash and SRAM

Most of the modules like ESP32 Wroom use external Flash-W25Q32 (4M Bytes!) for storing the application code. The chip supports 4 x 16 MBytes of external QSPI flash and SRAM with hardware encryption based on AES.

ESP32 accesses the external QSPI flash and SRAM through high-speed caches.

- Up to 16 MBytes of external flash are memory-mapped onto the CPU code space, supporting 8, 16 and 32-bit access. Code execution is supported.

- Up to 8 MBytes of external SRAM are memory-mapped onto the CPU data space, supporting 8, 16 and 32-bit access. Data-read is supported on the flash and SRAM. Data-write is supported on the SRAM.

Since the processor architecture is 32 bit. The internal peripherals, the wifi, Bluetooth, External Memories etc are mapped to 2^32 (4GB) address space.

Also one interesting thing to note is that the both processors are mapped symmetrically to this address space. It basically means, a register for example can be accessed from same address location from both the CPUs as shown in image below.

So looking at these features form the project/product development perspective, you can do away with an external micro-controller/Arduino. However it brings complexity of switching between the processors and handling the application data. It will not be a one way street as with normal micro-controller development. We will be exploring this in the numerous tutorials that we plan to do.

The WiFi

ESP32 implements TCP/IP, full 802.11 b/g/n/e/i WLAN MAC protocol, and Wi-Fi Direct specification. This means ESP 32 can speak to most of the WiFi Routers out there when used in station(client) mode. Also it is able to create an Access point with full 802.11 b/g/n/e/i.

ESP32 also supports the Wi-Fi Direct . Wifi-Direct is good option for peer-to-peer connection without the need of a access point. The Wifi-Direct is easier to setup and the data transfer speeds are much better than bluetooth. This could potential be used to configure ESP32 based projects from a phone/tablet that supports WiFi direct. There is no code example in the ESP-IDF SDK at the time of the writing. The ESP-IDF WiFi implementation has following features in the development:

- Infrastructure BSS Station mode / P2P mode / softAP mode support

- P2P Discovery, P2P Group Owner, P2P Group Client and P2P Power Management

- WPA/WPA2-Enterprise and WPS driver

- Additional 802.11i security features such as pre-authentication and TSN

- Open interface for various upper layer authentication schemes over EAP such as TLS, PEAP, LEAP, SIM, AKA or customer specific

- Clock/power gating combined with 802.11-compliant power management dynamically adapted to current connection condition providing minimal power consumption

- Adaptive rate fallback algorithm sets the optimal transmission rate and transmit power based on actual Signal Noise Ratio (SNR) and packet loss information

- Automatic re-transmission and response on MAC to avoid packet discarding on slow host environment

Bluetooth Classic and Bluetooth Low Energy(BLE)

ESP32 not just supports the latest BLE Bluetooth 4.2, it also supports classic bluetooth. It basically means it can speak to old and new bluetooth phones/tables. This could one of the best features especially, if you're designing a device that needs to work with existing as well as new phones/tablets in the market. The ESP32 Bluetooth Radio and Baseband supports the following features:

- Class-1, class-2 and class-3 transmit output powers and over 30 dB dynamic control range

- π/4 DQPSK and 8 DPSK modulation

- High performance in NZIF receiver sensitivity with over 98 dB dynamic range

- Class-1 operation without external PA

- Internal SRAM allows full speed data transfer, mixed voice and data, and full piconet operation

- Logic for forward error correction, header error control, access code correlation, CRC, demodulation, encryption bit stream generation, whitening and transmit pulse shaping

- ACL, SCO, eSCO and AFH

- A-law, µ-law and CVSD digital audio CODEC in PCM interface

- SBC audio CODEC

- Power management for low power applications

- SMP with 128-bit AE

Classic Bluetooth Link Controller Features

- Device Discovery (inquiry and inquiry scan)

- Connection establishment (page and page scan)

- Multi connections

- Asynchronous data reception and transmission

- Synchronous links (SCO/eSCO)

- Master/Slave Switch

- Adaptive Frequency Hopping and Channel assessment

- Broadcast encryption

- Authentication and encryption

- Secure Simple Pairing

- Multi-point and scatternet management

- Sniff mode

- Connectionless Slave Broadcast (transmitter and receiver)

- Enhanced power control

- Ping

Bluetooth Low Energy Link Controller Features

- Advertising

- Scanning

- Multiple connections

- Asynchronous data reception and transmission

- Adaptive Frequency Hopping and Channel assessment

- Connection parameter update

- Date Length Extension

- Link Layer Encryption

- LE Ping

Built-in Periherals

The built-in features of ESP32 are simply mind-numbing. These are more than any micro-controller that I've ever used till date in a single project. So the features are simply listed below. A lot can be done with these, and these will receieve special treatment with numerous tutorials in the days to come.

- Timers and Watchdog

- Real Time Clock

- ADC and built-in Sensors

- Digital to Analog Convertor (DAC)

- Touch Sensor

- Ultra Low Power(ULP) Co-processor

- Ethernet MAC Interface

- SD/SDIO/MMC Host Controller

- Universal Asynchronous Receiver Transmitter (UART)

- I2C Interface

- I2S Interface

- SPI Interface

- Infrared Remote Controller

- Pulse Counter

- Pulse Width Modulation (PWM)

- Hardware Accelerator

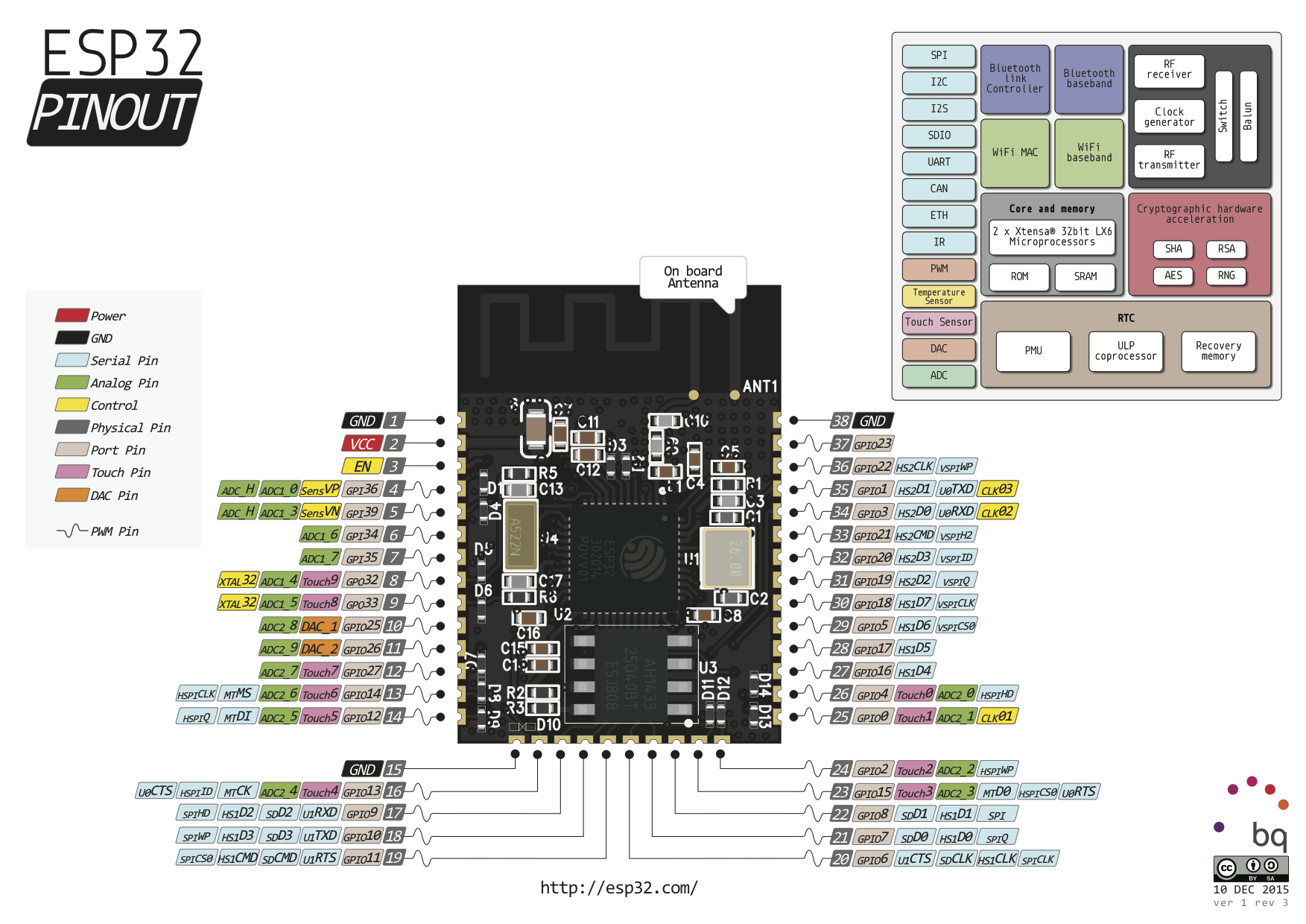

Package and Pinout

All the features we have looked so far, all packed in 48 pin QFN package size 6mm x 6mm.

[Image here]

A better picture to look at is the pinout diagram for the ESP Wroom32 breakout.

Image courtesy: Alberto (aka PighiXXX)

Image courtesy: Alberto (aka PighiXXX)

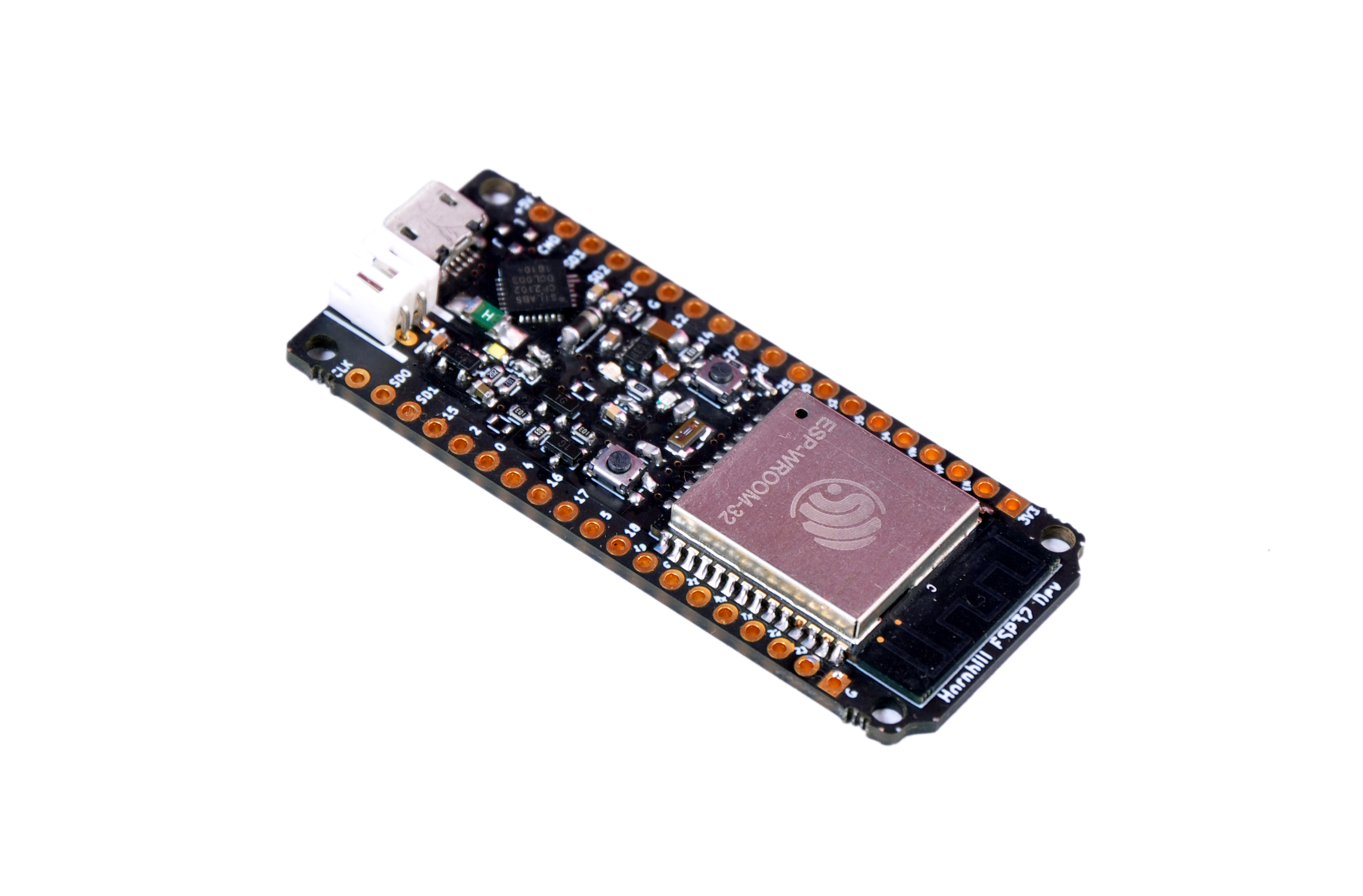

We plan to make several boards with ESP32. We are currently working on Hornbill ESP32. It is based on Wroom32 and comes with a built-in single cell LiPo charger.

ESP32 is power packed with hardware features. The high speed dual core processors along with the numerous built in peripherals it is set to replace micro-controllers in connected products. The WiFi, Bluetooth Classic and BLE make it great choice to build anything connected. Even if a project does not require a particular feature initially, it could be utilized as required. The built-in hardware accelerator enables secure code storage and securely connecting to the Internet with TLS (SSL). Apart from this the "out of the box" peripheral like the Infrared Remote Controller will be used in numerous hacks!

The software/firmware will be key to success of ESP32. It uses freeRTOS to handle multitasking. The number of peripherals, wireless connectivity, dual core processors and the overall architecture needs to be understood thoroughly to build reliable, responsive , secure and robust products and projects. We plan to do explore, it in depth. Signup to receive notifications as we go along building stuff with the chip of the future

[Update]

Some of you have also raised concerned about the reliability and WiFi performance of the chip for industrial grade applications. The specifications suggest that the chip should be able to perform well, however a lot depends on the hardware design of the end product. Also, while working on the previous version of the chip people had complained of the reset issues, digging deep we found out that several of these issues were improper structuring of the code. The chip uses RTOS to multitask, keep the WiFi stack refreshed. If certain rules are not followed during code it will result chip reset, wifi reset etc. In one of the tutorials we will try and cover this aspect. So remember if the chip is behaving erratic, it could be code as well.